Hello,

I have to use a slave SPI communication on the am3357 chip.

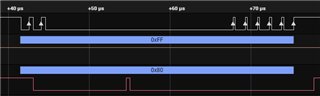

The master signal I receive is uneven. It is generated by software from the client side, and suffers from interrupt, see enclosed document.

The master SPI generates a clock around 700kHz. After 2 bits, the master stops for about 20µs, then resume the last 6 bits.

Because of this delay, I loose completely the transmission. The client cannot change anything on his code (of course).

1) Is there a way to make this kind of transmission work?

2) Is there a register to read if this error occurs, so I can clear the interrupt to start clean all over again?

I thank you in advance,

I wish you an excellent day,

Best regards,

Vincent SERTORIO