As shown below, TRM (page 4980) describes the timing of FIFO underflow interrupt generation.

"If you read when FIFO is empty, it will trigger an underflow interrupt."

However, when we tried on EVM, the FIFO underflow interrupt did not occur.

Can you please provide a sample code that actually generates a FIFO underflow interrupt?

Also, if there are any other triggers for FIFO underflow interrupts other than the above, please let us know.

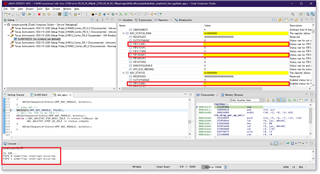

attach a screen capture.

attach a screen capture.