Other Parts Discussed in Thread: TDA4VH

Application:Two TDA4VH chips connect the MAC to MAC through the RGMII interface of the main domain;The PCB trace lengths of the TX / RX / CLK channel are about 8000 mil.

Problem:

-

The 100 Mbit/s communication is normal

-

The 1000 Mbit/s communication is failed

Test:

The oscilloscope measurement shows that the TX data signal cannot be reached chip's level threshold;

First:

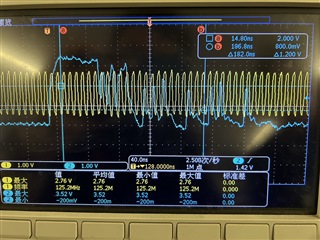

As shown in the figure below, data 01 is followed by 11, resulting in the level of 0 being raised. Similarly, 10 is followed by 00, resulting in 1 level being pulled down.

Second:

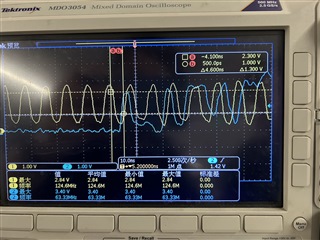

Through the IBIS simulation model and extracting the S parameters of the PCB board for simulation analysis, the simulation results are not very poor and can meet the high and low threshold of the signal.But the signal measured by high-speed oscilloscope is really poor (The test position of the probe is at the via of the chip at the receiving end, and the GND is very short); At present, it seems that the IBIS simulation model is inconsistent with the actual test.

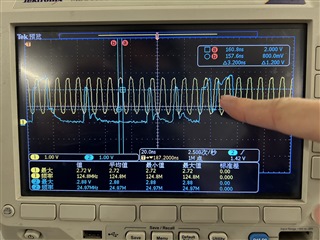

Then We disconnect the load and measure the TXCLK signal at the chip sending source. It is found that the slope of the rising edge of the clock waveform is very slow; Is this the lack of drive capability of the chip itself?

The above image measurement position is at the source disconnection string resistance,the trace of the 8000mil PCB has been disconnected,the measurement point is about 400 mil away from the chip.

In view of the above phenomena,we have two questions:

1.In our experience,RGMII pin locate at MCASP BANK.Too many multiple functions may produce more capacitive reactance.Is the problem caused by the backflow current between the multiplexed pins?

2.Is there any other method to improve drive capability.