Other Parts Discussed in Thread: SYSCONFIG

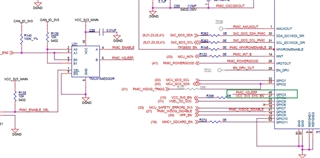

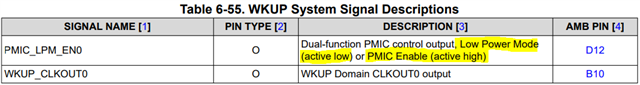

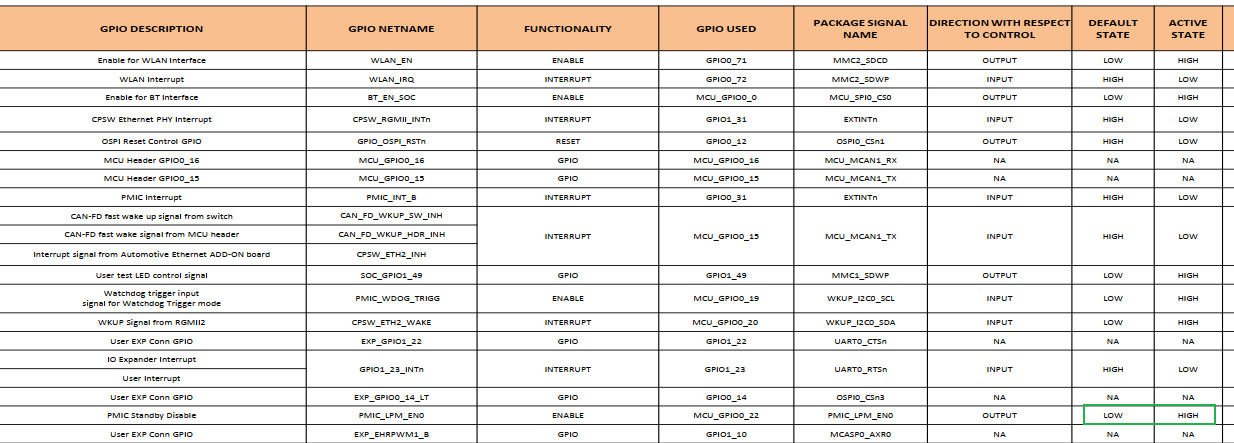

According to the figure, PMIC_LPM_EN0 is default low after reset. J9=floating,for U31, SEL=1,A=A1=PMIC_LPM_EN0=low, why PMIC don't switch to OFF state since enable/nPWRON PIN gets LOW. Is the PMIC configured in First Supply Detection (FSD) mode during power-up? Is GPIO3 configured as NSLEEP PIN for default,or the NSLEEP1B and NSLEEP2B register bits are configured in place for the function. If GPIO3 is configured as NSLEEP PIN for default, which one has been chosen? NSLEEP1 or NSLEEP2.