Other Parts Discussed in Thread: AMC7812

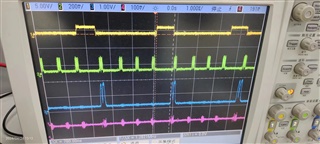

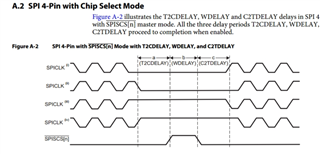

In the DEMO program, SPI_SPIFMT.WDELAY does not have a time set, and the default value of the register is 0. And with the default value of 0 for SPI_SPIDAT_1 WDEL, why does the CS switching time for each frame of data take 780ns?

Now the core board circuit is fully encapsulated, not open to the public, and cannot be rectified. We directly introduce SPI data cables from the core board circuit for timing testing. Now I want to know why the hardware circuit is not executed according to the software settings?

Our project now requires an interruption time of 3.3us to complete multiple SPI controls, and this delay in project design cannot be accepted

Suspect that there is a delay when the CPU accesses the external device. Every time the transmission is retransmitted, there is a certain delay between the CPU and the external device. Is it due to internal limitations of the CPU.