Tool/software:

Hi experts

I am currently working on Bringp for am62p. Due to the difference between DDR and the development version, it needs to be reconfigured using the official DDR configuration tool

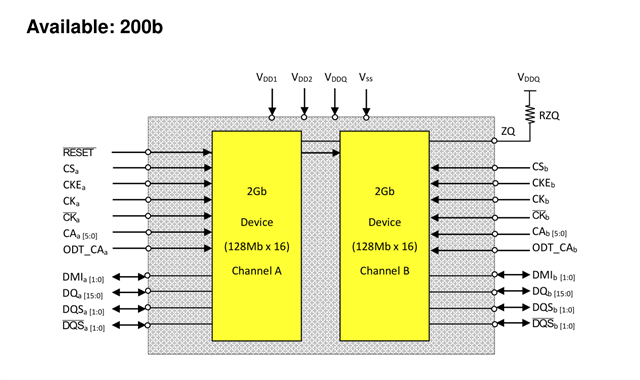

DDR still cannot work properly. DDR uses South Asian DDR .the DDR size of 512M. The DDR model is NT6AN128T32AC-J1H. the am62p SDK version: 10.00.

The specific information is as follows:

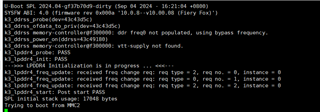

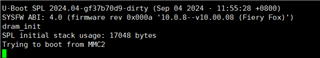

1.Serial port printing is as follows:

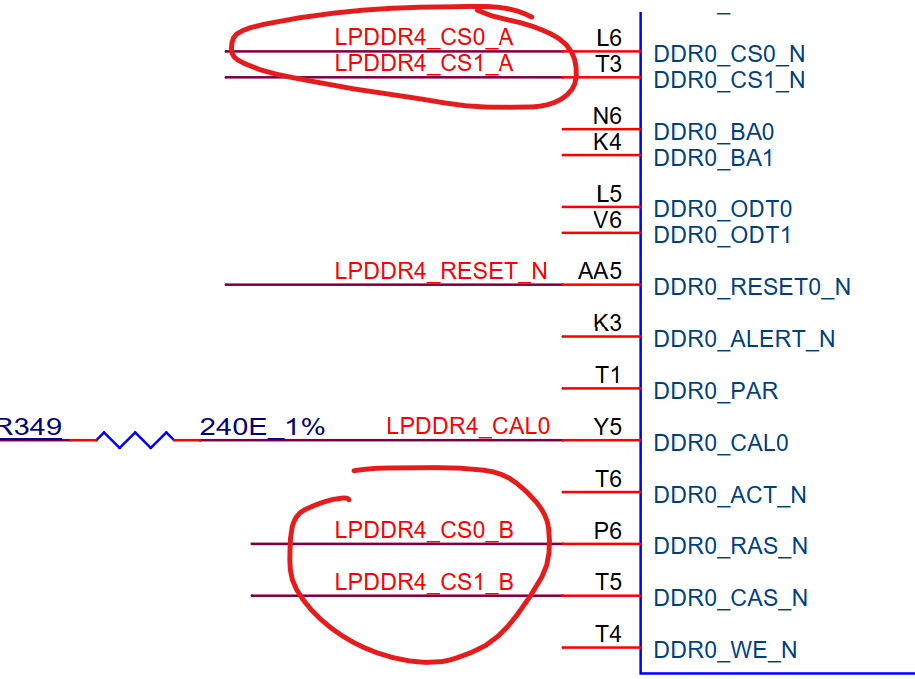

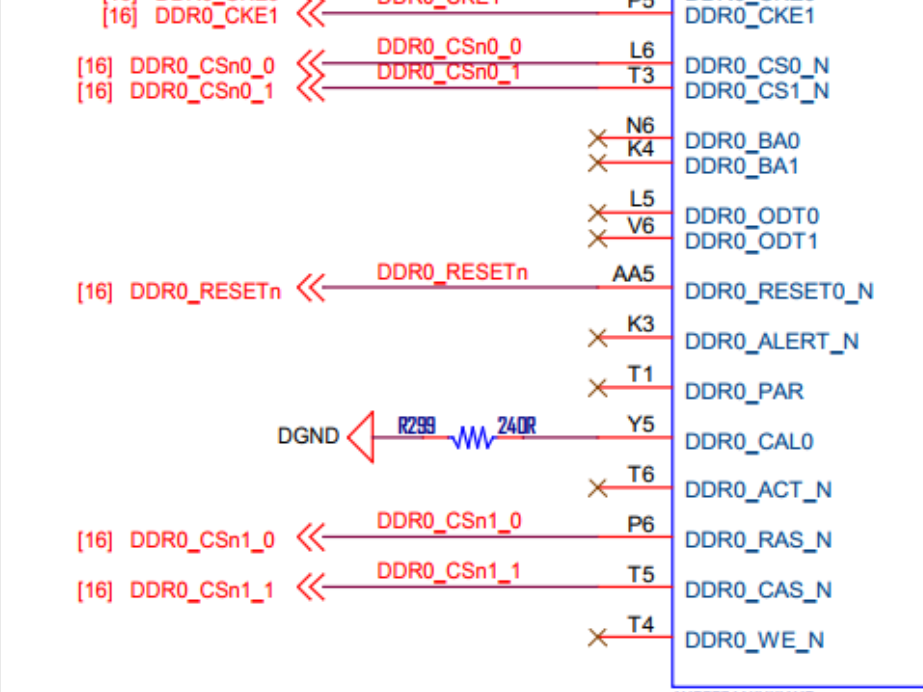

2.The schematic diagram of DDR is as follows:

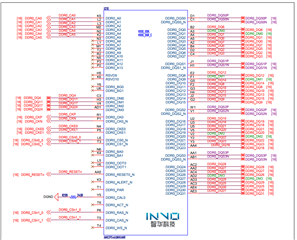

3.The DDR configuration file is as follows: