Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

I have a functional PCIe setup with the AM64x running Linux on the A53 as the Root Complex and an FPGA board as the Endpoint. From the AM64x (RC), I can successfully detect the FPGA (EP) and perform read/write operations on the registers and BAR memory.

As discussed and with reference to the TMDS243EVM: PCIE: RC read EP Bar info stuck. 243EVM+Intel FPGA - Arm-based microcontrollers forum - Arm-based microcontrollers - TI E2E support forums, I followed the suggested steps as below. However, the issue still persists that the ‘PCIe link is not up, and the LTSSM remains in the 0x00 (detect) state’.

- FPGA board is directly plugged-in to the AM64x PCIe connector.

- Followed the AM64x MCU+ SDK: PCIE buffer transfer RC example.

- Removed the jumper J34 on the AM64x.

- Verified the PCIe REFCLK using oscilloscope at the ‘AM64x(RC) PCIe connector(A side pin 13 & 14)’ and FPGA(EP) as well. It is coming 100MHz at both RC and EP.

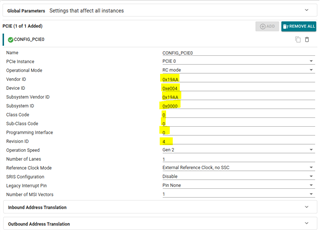

The images below show the configuration of the PCIe IP in the FPGA and the PCIe peripheral in the AM64x R5 using SysConfig, respectively. Please review them and let me know if they are correct.

For the AM64x as the Root Complex, should the highlighted parameters be set to the 'Endpoint' configuration values or the local Root Complex configuration values?