Tool/software:

Hi Experts

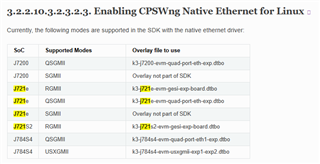

I was reviewing the documentation for enabling CPSWng Native Ethernet for Linux in the latest Processor SDK (10.01.00.04), and I noticed that the J721e SoC is listed as supporting only RGMII and QSGMII modes. The overlay files for these modes are provided (k3-j721e-evm-gesi-exp-board.dtbo and k3-j721e-evm-quad-port-eth-exp.dtbo). However, it seems that SGMII support is marked as "Overlay not part of SDK."

Could you confirm whether J721e supports SGMII MAC ports in the current SDK? If it is not supported directly, is there any plan for future support, or would I need to customize the device tree and drivers to enable it?

Thanks in advance for your help!

BR

Jay