Tool/software:

U-Boot 2024.04-ti-ga970f6e51043 (Nov 13 2024 - 14:26:23 +0000)

=> sf update ${loadaddr} 0 0x1000000

device 0 offset 0x0, size 0x1000000

16777216 bytes written, 0 bytes skipped in 98.316s, speed 174762 B/s

Does anyone have tips to improve the speed?

I found I can manually write blocks as long as I erase first. However it is still slow. 1 minute to erase. 45 seconds to write.

=> sf probe

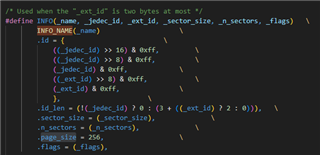

SF: Detected s28hs512t with page size 256 Bytes, erase size 256 KiB, total 64 MiB

=> sf erase 0x0 0x1000000

jedec_spi_nor flash@0: at 0x0, len 16777216

SF: 16777216 bytes @ 0x0 Erased: OK

=> sf write 0x80000000 0x0 0x1000000

device 0 offset 0x0, size 0x1000000

jedec_spi_nor flash@0: to 0x00000000, len 16777216

SF: 16777216 bytes @ 0x0 Written: OK

Driver in the device tree is jedec,spi-nor nested under "ti,am654-ospi", "cdns,qspi-nor"

Files are cadence_qspi.c and sf_dataflash.c, so I'll start debugging there...

I see a lot of changes in cadence_qspi.c for 2025 next. Does anyone know if this should be fixed?

For example: git.ti.com/.../spi

I applied, recompiled, and verified these patches do not fix either of these issues.

It also appears the changes may introduce a new bug where erase/update no longer work too.

Datasheet lists 898KBps writes and 331KBps erase.