Tool/software:

Hi,

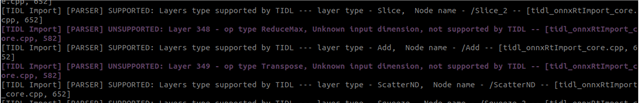

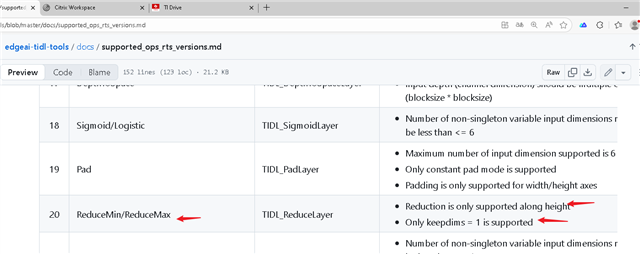

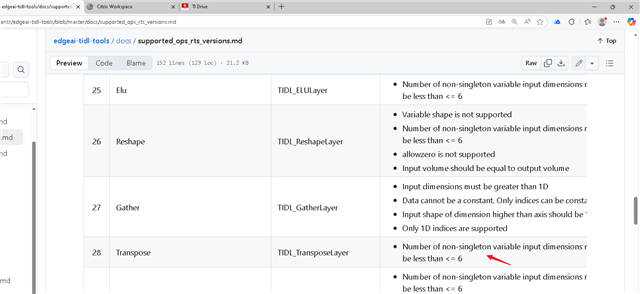

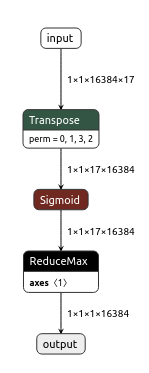

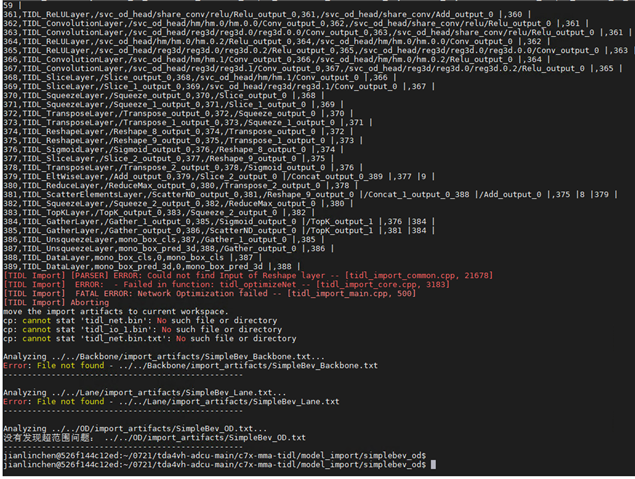

We are using tidl to export the model, but the model export failed, the log is as follows.

The TIDL version is 11.01.04.01.

The compressed file named E2E.zip, which contains the model and export config, has been uploaded to tidrive.ext.ti.com/.../100ec4b5-b2a9-4e4b-9208-f38f41488a4b

Thanks