Our customers are designed by reference to EVM(TMDSEVM6678L) with CC6671.

Our customers are designed by reference to EVM(TMDSEVM6678L) with CC6671.

But she is considering not using the CDCE62005 Clock IC because target b/d size issue.

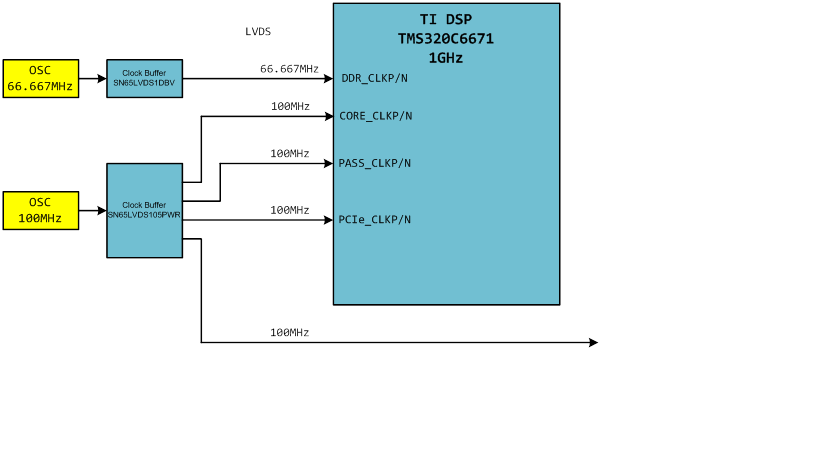

So she will use the below concepts.

Is there no problem When the DDR Clock & Core Clock of DSP each input independently?

I would like to know what to consider when she use this.