Tool/software: Code Composer Studio

Hi,

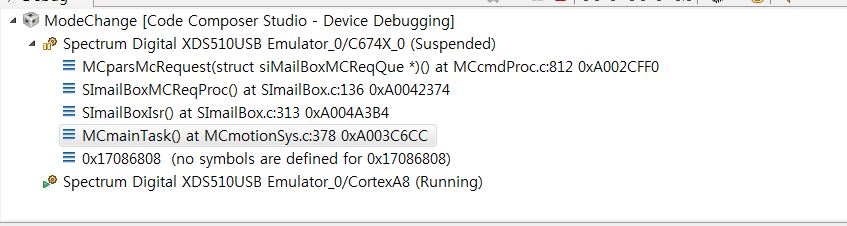

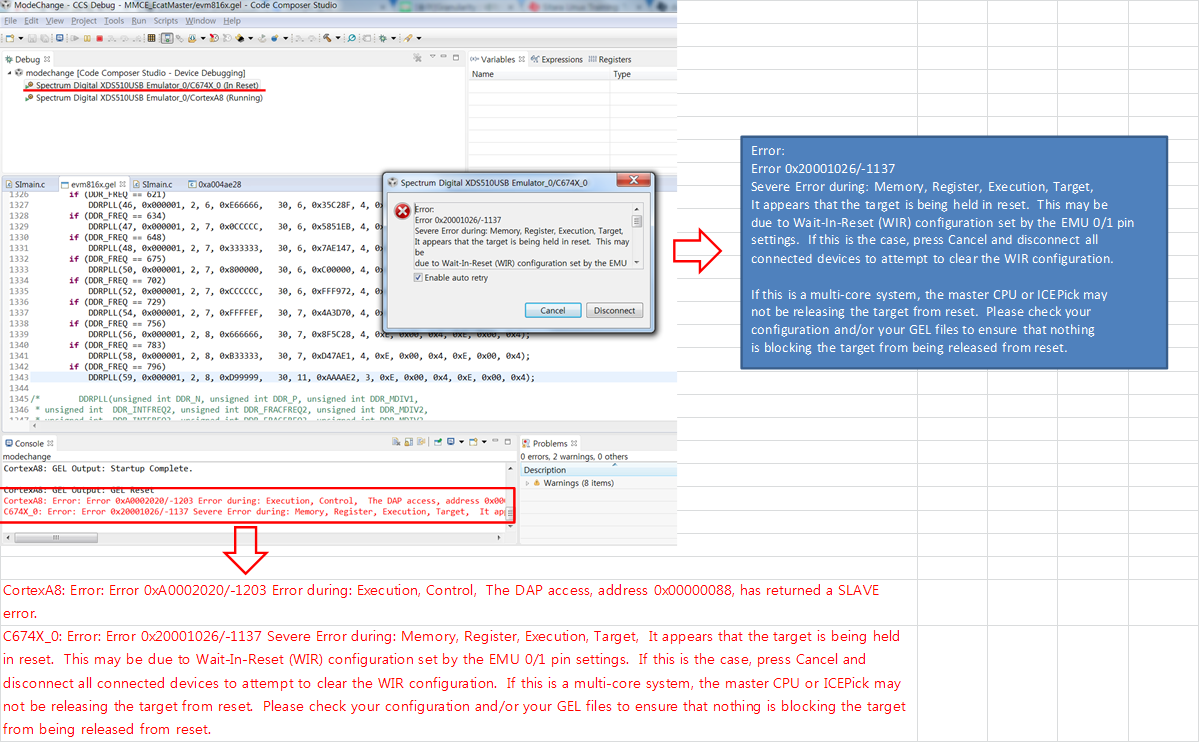

I have a problem like below picture. It suddenly occurred while running firmware few hours. I don't use any OS (such as TI RTOS).

I don't know why it occurred and how I debug to fix this. I have several boards, but they did not occur the problem except one. Only one board had this issue.

Please help me to reply any comment, If you have any idea about this.

Thank you in advance.