Hello, I am using TMS320C6415 and have an intermittent issue where the device hangs during power up and does not complete the boot process. The issue occurs at all temperatures. I have attempted to attach an emulator to read the EMIFB and EDMA registers but I am unable to connect to the device when it is in a failed state. The device bootmode is set to EMIFB 8-bit ROM boot. The EMIFB input clock is set to CPU/4 Clock rate. The failure appears to happen either at the end of the 1K byte transfer from Flash using the internal boot loader, or somewhere in the middle of the second boot transfer from flash that is setup using the code that is contained in the first 1K bytes that is transferred using the internal boot loader. The flash device is PC28F256M29EWLA. Below are logic analyzer captures at the end of the 1K boot transfer for a passing and failing condition. In a failing condition, the DSP device drives EMIFB_WE_L active. This signal should not be active as the device is still in the process of reading boot code from the flash device. The reset to the DSP device is being driven from an FPGA. During power on the reset is held in the active state through a reset monitor, then after the FPGA configures it drives a reset pulse to the DSP that occurs 50 ms after power on reset, the reset pulse is about 800 us wide. Any help on where to look or what would cause the DSP to intermittently drive EMIFB_WE_L active during the boot process would be greatly appreciated, thank you.

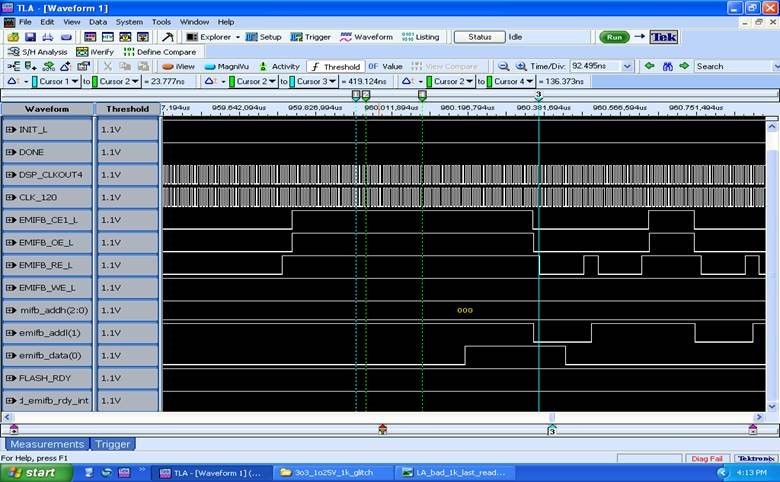

Passing condition at end of 1K byte boot transfer, secondary boot transfer starts:

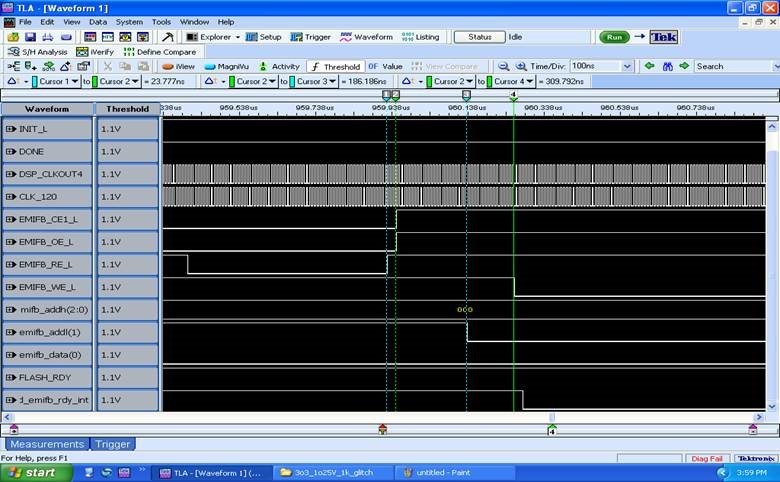

Failing condition, EMIFB_WE_L drive low for unknown reason at end of 1K boot transfer, secondary boot transfer never starts: