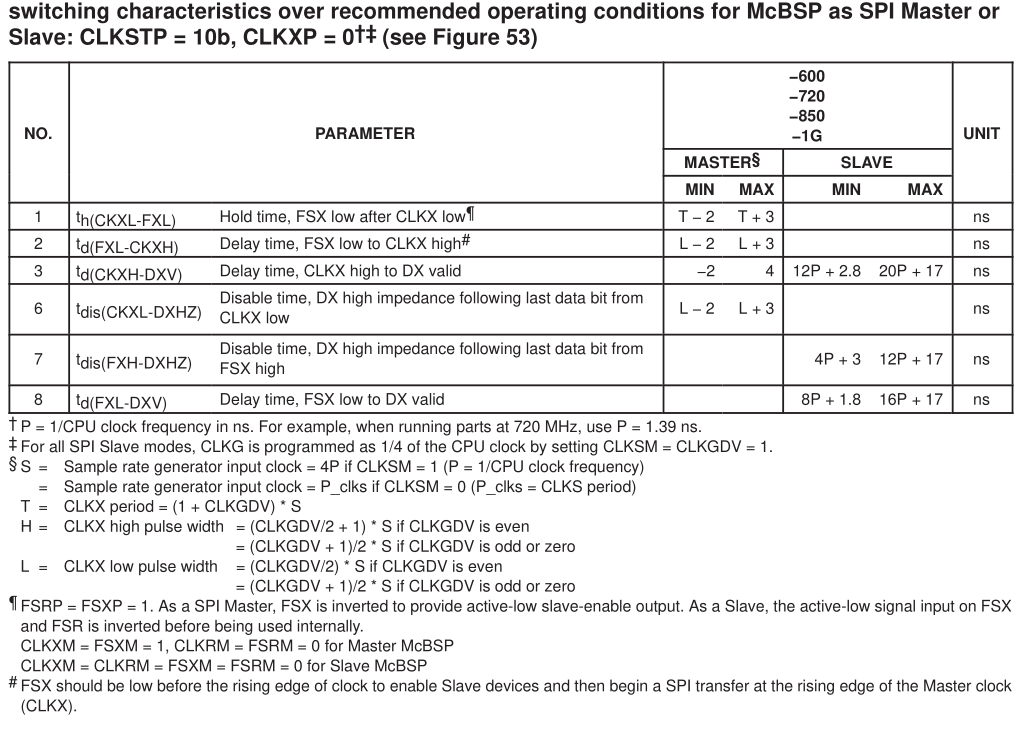

For SPI port as a slave, in any mode, the data sheet defines the Dx valid delay from Clock parameter as:

12P + 2.8 min, and 20P + 17 max, where P is the period of the internal DSP clock.

For Dx valid delay parameter definition, are the constant terms (2.8, 17) dependent on temperature and die variations only? If not what are the dependencies?

For Dx valid delay parameter definition, are the "P" terms (12P , 20P), is the variation (12 - 20) a function of internal DSP timing with the SPI port only? is this variation seen for all SPI configurations? Or is it tighter in some configurations? Can this "P" term be characterized for SPI configuration, DSP configuration and/or temperature environment?