Other Parts Discussed in Thread: TDA2,

Tool/software: Code Composer Studio

Hi,

I am trying to boot up TIDEP-01017 TDA2 via CCS and am following the steps provided in the Application Report SPRAC17B. I set the boot mode on SW4 to 6'b000000 as per the Technical Reference Manual SPRUI29F

The tda2xx_cascade_bios_radar build that is provided in the processor sdk package does not use A15 has the host processor, so I bypassed it in the ccxml launch file. When I try to connect Cortex_M4_IPU1_C0, I get an error as below:

Error connecting to the target:

(Error -1170 @ 0x0)

Unable to access the DAP. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK).

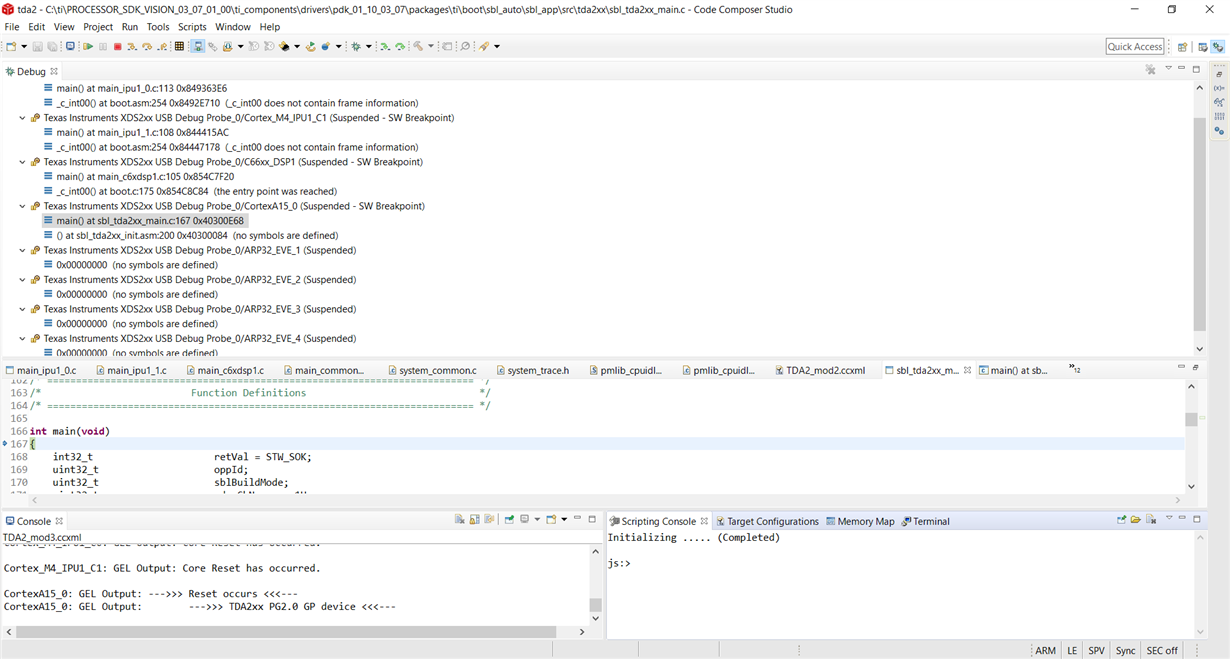

However, when I add back A15 as the host processor and connect to it first, then enable all cores from Scripts > TDA2xx_MULTICORE_Initialization > TDA2xx_MULTICORE_EnableAllCores and then connect to Cortex_M4_IPU1_C0, it is able to connect.

I subsequently connect to all the remaining processors and load corresponding binaries. However, since A15 binary was not compiled, I do not load it. Is this ok?

Also, once this is done I hit Resume on each of the processors and I see the below prints on the console:

[Cortex_M4_IPU1_C1]

MAC Port 0 Address:

b4-52-a9-63-38-7a

MAC Port 1 Address:

b4-52-a9-63-38-7b

Network Added: If-1:192.168.1.200

Service Status: Telnet : Enabled : : 000

[Cortex_M4_IPU1_C0] IPU1-0 Remote Log Shared Memory @ 0xbfb200a0

IPU1-1 Remote Log Shared Memory @ 0xbfb2e8a0

HOST Remote Log Shared Memory @ 0xbfb310a0

DSP1 Remote Log Shared Memory @ 0xbfb360a0

DSP2 Remote Log Shared Memory @ 0xbfb388a0

EVE1 Remote Log Shared Memory @ 0xbfb3b0a0

EVE2 Remote Log Shared Memory @ 0xbfb3d8a0

EVE3 Remote Log Shared Memory @ 0xbfb400a0

EVE4 Remote Log Shared Memory @ 0xbfb428a0

IPU2 Remote Log Shared Memory @ 0xbfb450a0

However, I still do not see the TDA2 boot up via UART terminal. Is there any step I am missing? How do I step through the code once boot up is done?

Thanks,

Siddharth