Other Parts Discussed in Thread: TDA2, MMWCAS-DSP-EVM, AWR1243

Hi,

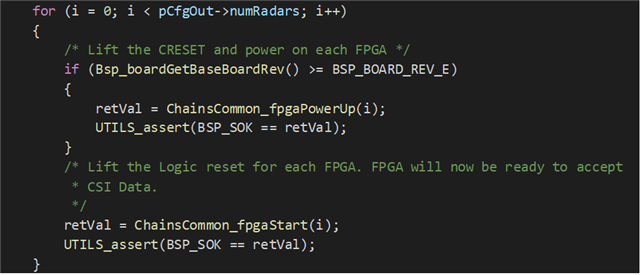

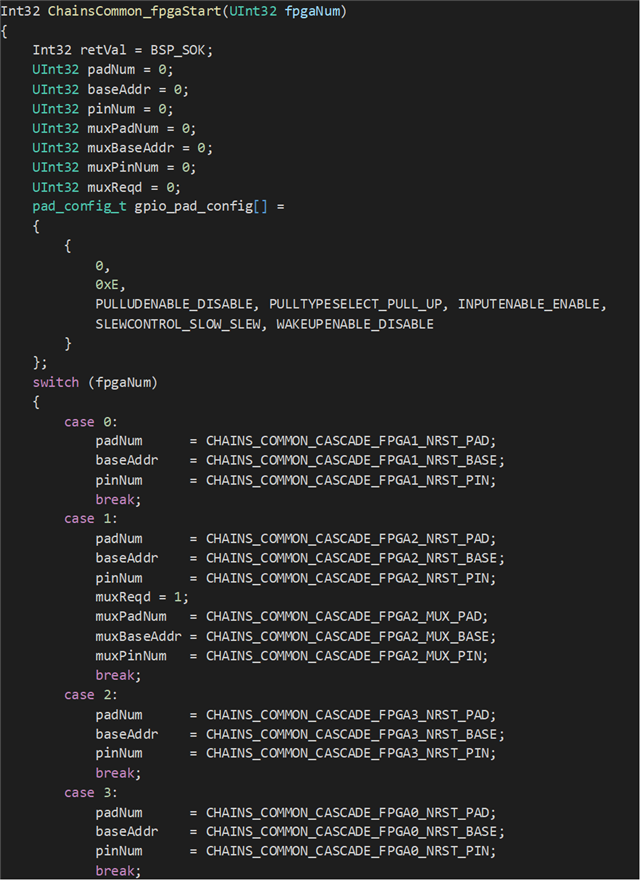

We are trying to bring up one of our custom boards that uses two AWR1243 in cascade mode. This is interfaced with a TDA2 board (MMWCAS-DSP-EVM). Our initial tests with mmWave Studio 02.01.00.00 have all been successful. We are now wanting to move to an online data acquisition / data processing pipeline. We are using Processor SDK 3.7 Radar package for this purpose. We use one of the sample use cases provided as our starting point and customized it to enable our 2-chip cascade setup. However we are observing that data from one of the chips (slave device) is not entering the data processing chain.

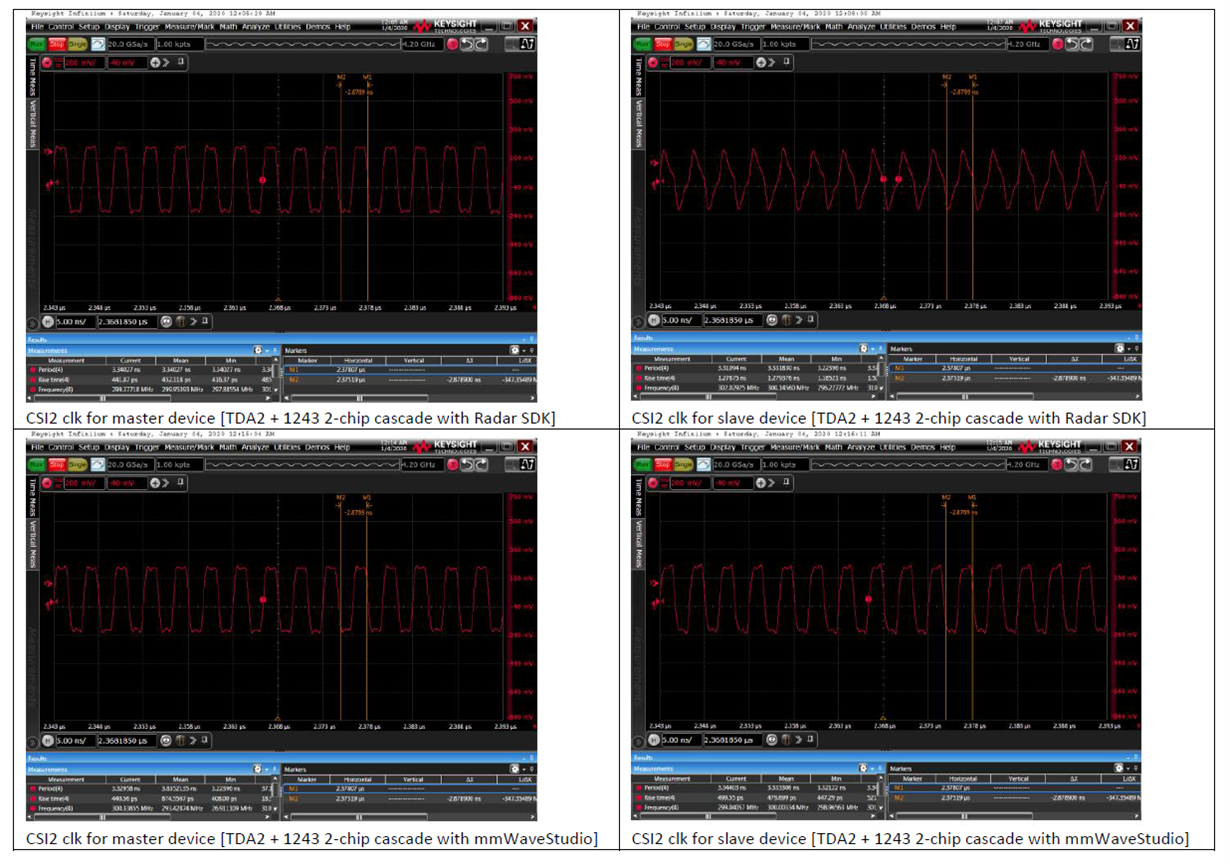

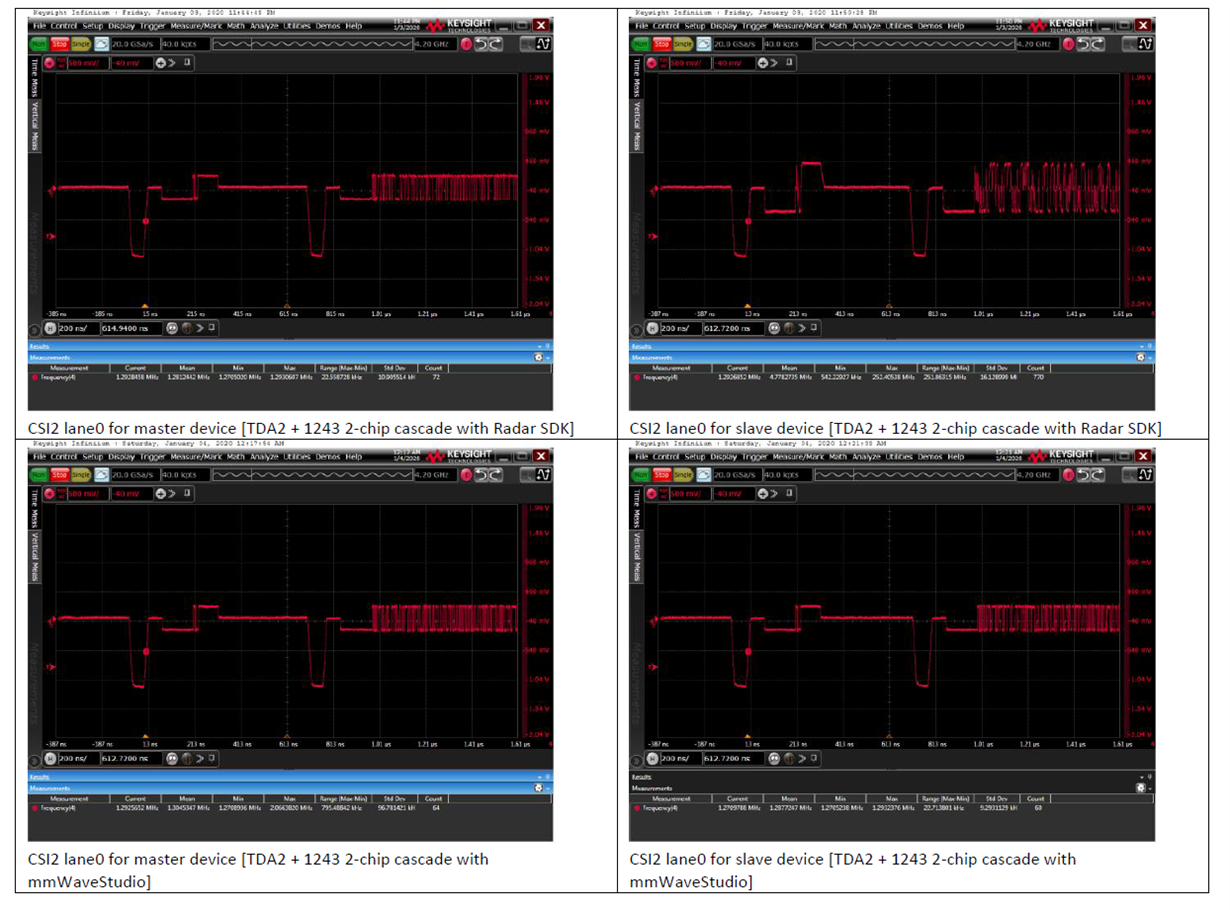

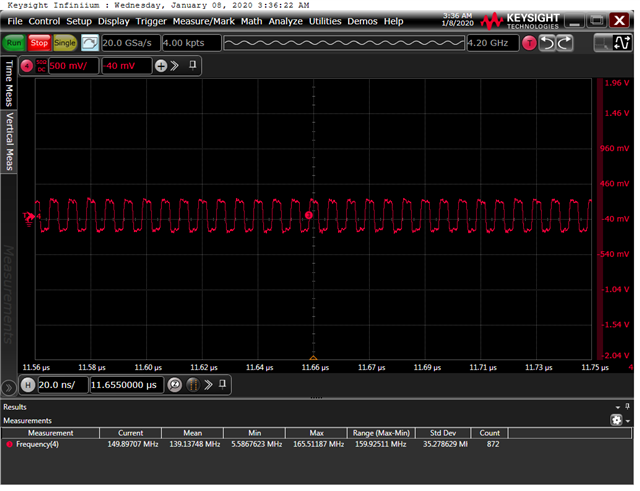

We probed the CSI-2 lanes on both the devices and identified that the 300 MHz CSI-2 clock signal on the slave device is skewed when compared to the master device. More specifically, the rise time is observed to be ~1.3 ns on the slave device compared to ~450 ps on the master device. The same experiments when using mmWave Studio produce very similar CSI-2 clocks (rise time of ~440-500 ps) on both master and slave devices, which leads us to believe that some configuration in the Radar SDK is causing this issue. Please see below screenshots of the measurements captured.

Could you please advice as to what could be causing this discrepancy when we switch software frameworks?

Thanks,

Siddharth