Hi,

We are using TMS320C6652,

GPIO[13:1] configured for SPI Boot Mode,

As PCIESSMODE[1:0]/GPIO[15:14], and PCIESSEN/TIMI0) are reserved for C6652 ,we have left these pins floating.

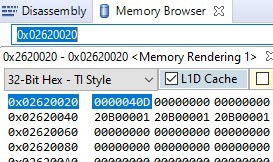

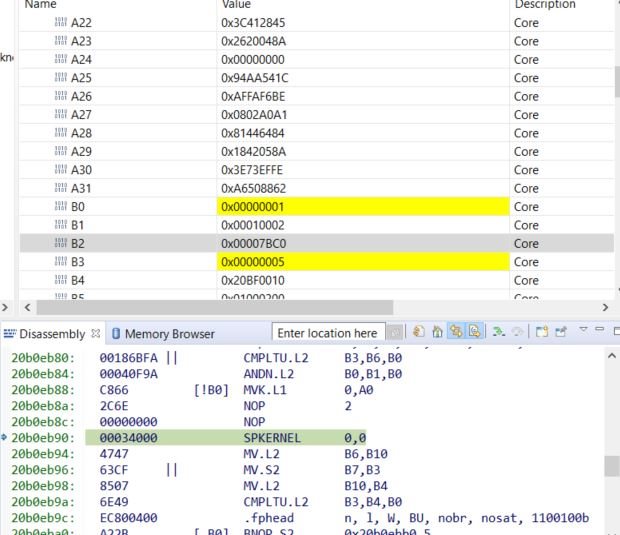

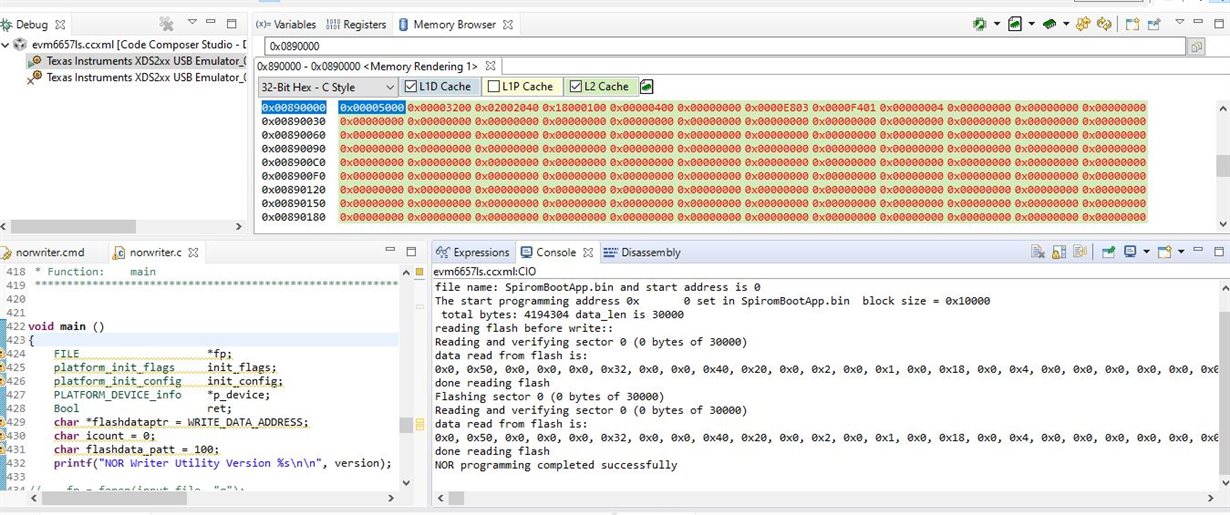

We flashed the SP platform application image from DSP (using Volatile Boot) to NOR flash and was able to verify the flash contents.

But when we power cycle the board with boot mode set to NOR SPI boot (boot mode 6) , RBL (Rom Boot Loader) TI firmware in chip supposed to load the image to SRAM and execute it. But this is not working .

Please suggest .

Regards,

Spandana.