Other Parts Discussed in Thread: TMDSEMU560V2STM-U

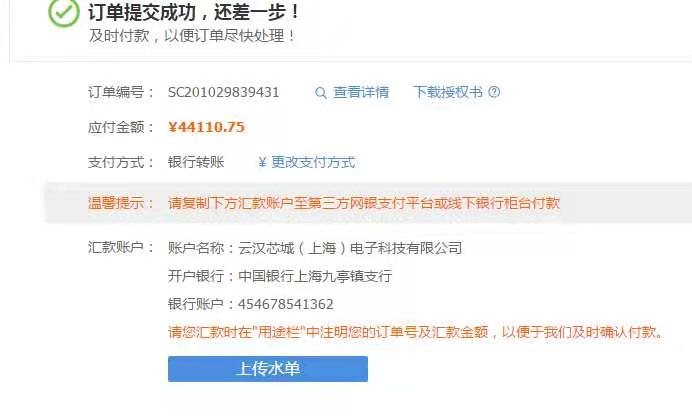

我们买了四个仿真器,分别是两个TMDSEMU560V2STM-UE(#1,#2),两个TMDSEMU560V2STM-U(#3,#4)。用了一段时间,有三个出了问题,只有一个还在正常使用中。(#1,#2,#3,#4是我给仿真器编的号)

四个仿真器出现的情况如下:

编 号#1:型号是TMDSEMU560V2STM-UE,是一个有源仿真器,接上电源和USB连线后,LED无任何响应(不亮,不闪),使用Sd560v2Config也无任何响应。

编 号#2:型号是TMDSEMU560V2STM-UE,接上电源和USB线后,LED正常闪烁并能进入正常状态,使用Sd560v2Config软件进行测 试,可以检测到仿真器,也可以进行USB回环测试,进行DbgJtag测试时, 第一个RESET项就不能通过,错误信息是:error-182,大意是连接电缆断开,但是反复检查,电缆都是好的,就是无法连接目标板。

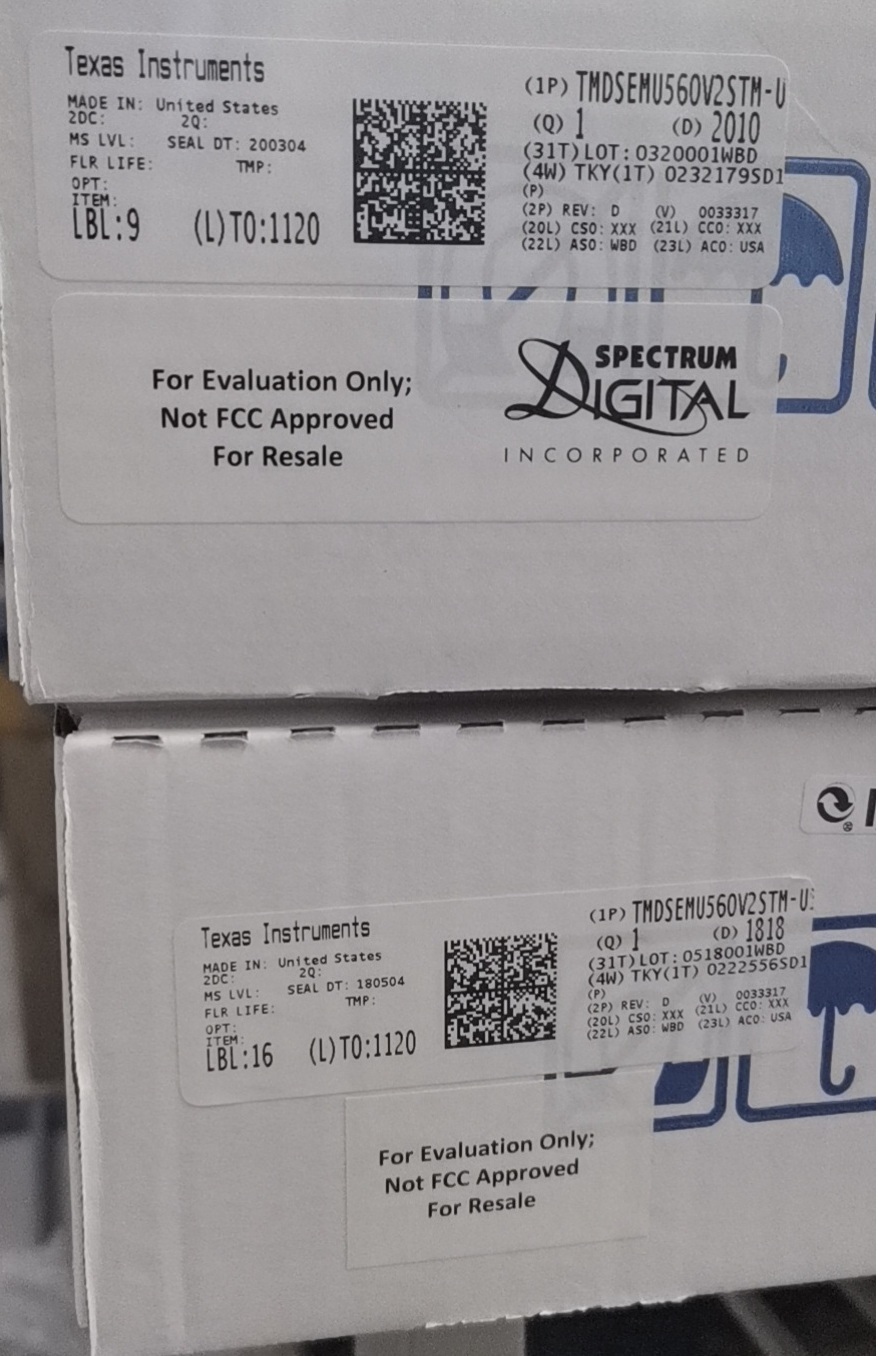

编 号#3:型号是TMDSEMU560V2STM-U,可以正常工作,正常连接目标板。使用Bh560v2Config Utility软件,可以检测到仿真器,并可以进行所有操作。

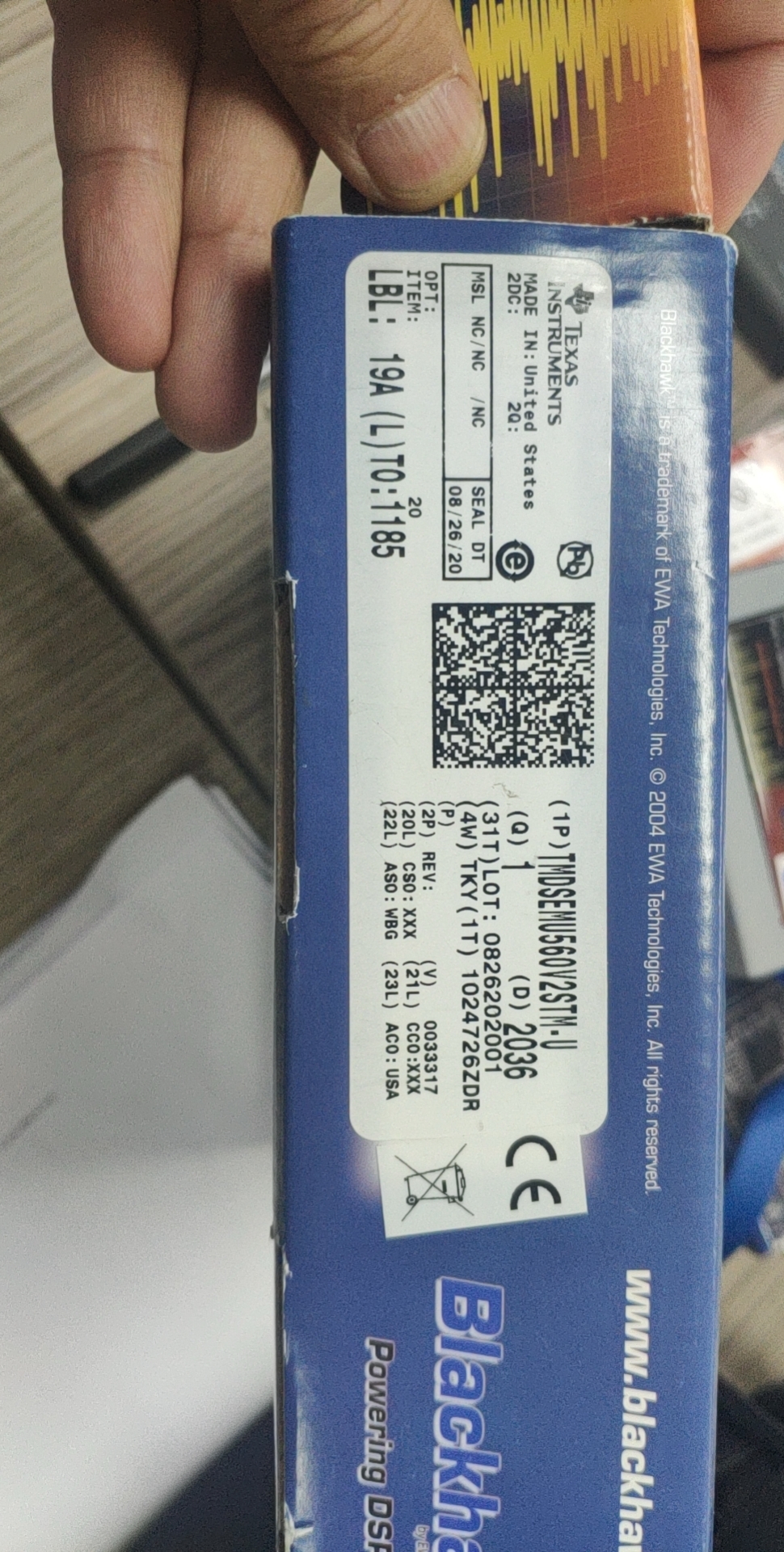

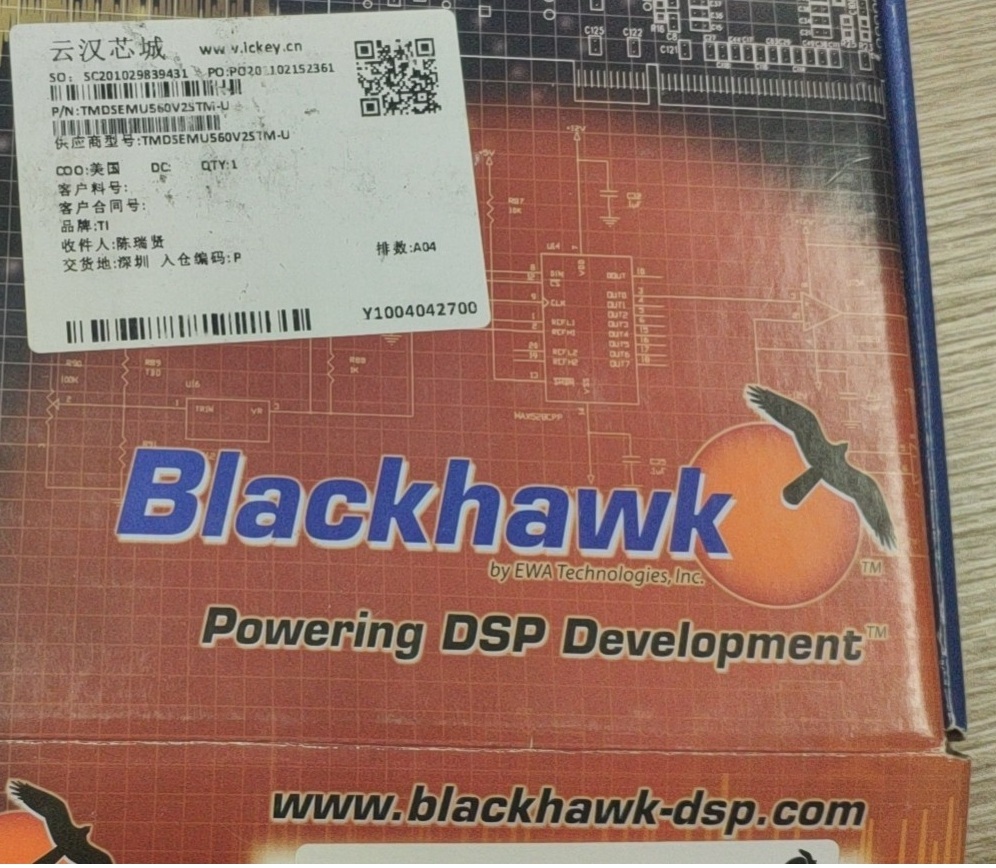

编 号#4:型号是TMDSEMU560V2STM-U, (BlackHawk ),连接USB电缆后,两个LED均不亮,使用Bh560v2Config Utility软件测试,不能检测到仿真器。

这个仿真器我反反复复进行测试了两三周了,也读了很多TI官网相关文件资料,始终无法取得任何进展,恳切希望您能帮忙解决我的问题。

同时,我觉得有这三个仿真器我自己是无法处理的,我希望能够将他们返厂维修,希望您能为我打开这个渠道,谢谢您。

附件为视频

We bought 4 emulations from www.ickey.cn, their models are TMDSEMU560V2STM-UE(#1,#2)and TMDSEMU560V2STM-U(#3,#4). Several days later, there are something wrong with 3 of them, only 1 of them can use normaly. ( I coding these 4 emulations with #1, #2,#3,#4)

Here are the situations of these emulations:

Coding number #1: Its model is TMDSEMU560V2STM-UE, it is a emulation with dedicate power supply. When I connect the power supply cable(power up) and USB cable, it has no any response, all LEDs are off. I test it with software 'Sd560v2Config', i got no response either.

Coding number #2: Its model is TMDSEMU560V2STM-UE also. I connect the power supply cable(power up) and USB cable, LEDs start blink and the emulations enters normal state.

I test it with software 'Sd560v2Config', the software detects the emulation. I'v done several tests with USB cable:

USB loopback : pass

USB print status: pass

USB force EEOS: pass

Then I use 'DbgJtag' test page test the emulation, I got a error info"error-182" when i use 'RESET' command. The explanation is:

The controller has detected a cable break that is near-to itself.

The user must connect the cable/pod to the controller.

I checked the cable for several times, there is nothing wrong with it.

Coding number #3: Its model is TMDSEMU560V2STM-U, it can work normal now. I am very glad that I still have a good emulation to work with my target board. Software 'Bh560v2Config Utility' can detect it , and passes every test.

Coding number #4: Its model is TMDSEMU560V2STM-U. No led become on when I connect the USB cable with it, no response! Software 'Bh560v2Config Utility' cannot find it.

I test these emulations for weeks, and I have read many technical documentations from TI website, but I got no progress. I fell exhausted!

I think I can't correct these errors. Maybe they should be returns to the factory and be repaired.

CAN you help me?

Thank you anyway.

I attach several visions as attachments.