Our custom board has several working serdes/sgmii interfaces, however one doesn't appear to work: I could use some guidance on what to investigate.

The errant interface is serdes 0 lane 1 (Sierra / 16-G), which we are configuring in PHY-less mode to another custom TDA4's using the exact same interface. At the SGMII level I have tried both AUTONEG_MASTER+AUTONET_SLAVE and FORCEDLINK modes with no luck, so I started looking at the lower level serdes configuration and registers.

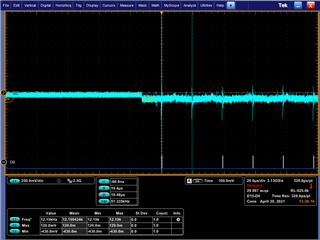

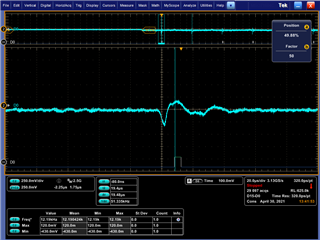

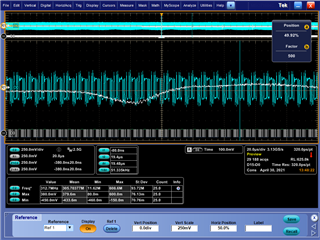

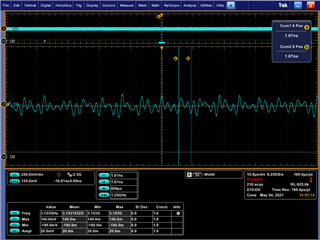

At the serdes level, I've observed that LANALIGN1 (0500 04C8h) on both sides is "hunting" for a value, indicating that it is unable to lock on to the signal from the remote side. While watching PHY_PMA_ISO_DATA_HI__PHY_PMA_ISO_DATA_LO_j (0500 F01Ch) I can disable the remote serdes using LANECTL1[31:30] and see a corresponding change from random values when enabled to just 0 when disabled.

What more should I investigate from here? Is there a way to configure the serdes to send only a single pattern and lock LANALIGN1 so I can observe the result in PMA_ISO_DATA?