Other Parts Discussed in Thread: AM5728, ADS7883

I have been doing DSP type development, trying to get ready before we produce our first board.

I have an AM5728 IDK board. I am doing some work to get the PRU to grab data from digitizers. Right now, this is a single ADS7883 ADC, but it will turn into an ADS9234.

I’m using PRU0 in the first ICSS unit. I have good PRU firmware and I generated an image:

const uint32_t PRU_adc_image_0[] = {

0x240000c0,

0x24010080,

0x0504e0e2,

…

I have been trying to get it to run while debugging from the first DSP c66x core:

(DSP code)

void PRU_init(void)

{

CSL_l4per_cm_core_componentRegs *l4PerCmReg = (CSL_l4per_cm_core_componentRegs *) CSL_DSP_L4PER_CM_CORE_REGS;

CSL_control_core_pad_ioRegs *controlCorePadReg = (CSL_control_core_pad_ioRegs *) CSL_DSP_CORE_PAD_IO_REGISTERS_REGS;

// volatile unsigned int *pruss_cgr = ((volatile unsigned int *)0x4B226010);

volatile unsigned int *pruss_syscfg = ((volatile unsigned int *)0x4B226004);

//Set pin mux mode to connect the PRU to external GPIO pins and enable inputs

CSL_FINS(controlCorePadReg->PAD_VIN1A_D5, CONTROL_CORE_PAD_IO_PAD_VIN1A_D5_VIN1A_D5_MUXMODE, 13U); // SPI CS

CSL_FINS(controlCorePadReg->PAD_VIN1A_D5, CONTROL_CORE_PAD_IO_PAD_VIN1A_D5_VIN1A_D5_INPUTENABLE, CSL_CONTROL_CORE_PAD_IO_PAD_VIN1A_D5_VIN1A_D5_INPUTENABLE_DISABLE); // SPI CS

CSL_FINS(controlCorePadReg->PAD_VIN1A_D6, CONTROL_CORE_PAD_IO_PAD_VIN1A_D6_VIN1A_D6_MUXMODE, 13U); // SPI CLK

CSL_FINS(controlCorePadReg->PAD_VIN1A_D6, CONTROL_CORE_PAD_IO_PAD_VIN1A_D6_VIN1A_D6_INPUTENABLE, CSL_CONTROL_CORE_PAD_IO_PAD_VIN1A_D6_VIN1A_D6_INPUTENABLE_DISABLE); // SPI CLK

CSL_FINS(controlCorePadReg->PAD_VIN1A_D7, CONTROL_CORE_PAD_IO_PAD_VIN1A_D7_VIN1A_D7_MUXMODE, 12U); // SPI Data

CSL_FINS(controlCorePadReg->PAD_VIN1A_D7, CONTROL_CORE_PAD_IO_PAD_VIN1A_D7_VIN1A_D7_INPUTENABLE, CSL_CONTROL_CORE_PAD_IO_PAD_VIN1A_D7_VIN1A_D7_INPUTENABLE_ENABLE); // SPI Data

//TODO maybe disable weak pull up/down on these as well

//Disable clock to PRUSS1 module (containing 2 PRU units)

CSL_FINST(l4PerCmReg->CM_L4PER2_PRUSS1_CLKCTRL_REG, L4PER_CM_CORE_COMPONENT_CM_L4PER2_PRUSS1_CLKCTRL_REG_MODULEMODE, DISABLED);

//memcpy firmware to the correct PRU instruction area of memory

memcpy((void *)CSL_DSP_PRUSS1_U_INST_RAM0_12KB_REGS, PRU_adc_image_0, sizeof(PRU_adc_image_0));

//Enable clock to PRUSS1 module (containing 2 PRU units)

CSL_FINST(l4PerCmReg->CM_L4PER2_PRUSS1_CLKCTRL_REG, L4PER_CM_CORE_COMPONENT_CM_L4PER2_PRUSS1_CLKCTRL_REG_MODULEMODE, ENABLE);

//Take PRU out of standby

*pruss_syscfg = (*pruss_syscfg & 0xFFFFFFF0) | (1<<2) |1;

}

The firmware does appear in the instruction memory for the correct PRU after I execute this.

However, it tends to say that the module is in standby still in the CM_L4PER2_PRUSS1_CLKCTRL register (0x00040000 bit).

This changed after I connected the debugger to the PRU and then back to the DSP.

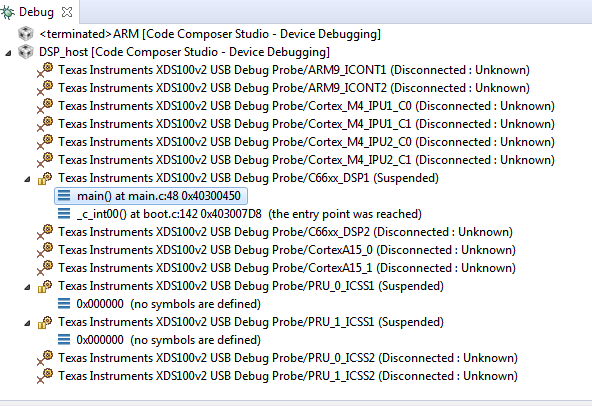

Still, it does not run. In fact, it says that the two PRU units on ICSS1 are (Suspended) in the eclipse debug window.

I feel that it is the IDE that is holding the two units in suspension. Am I right? What to do?

Thanks!

Blake