Hi guys,

My customer has the below question:

pdk_k2g_1_0_7

bios : 6.46.5.55

xdctools_3_32_01_22_core

I built a QSPI test SW based on QSPI_BasicExample_evmK2G_armTestProject to test my board. My QSPI component is the same as the QSPI on K2G EVM.

My test code uses three QSPI APIs: Board_flashEraseBlk, Board_flashWrite and Board_flashRead as followed in a infinite loop

ioMode = BOARD_FLASH_QSPI_IO_MODE_QUAD;

while(1)

{

Semaphore_pend(semQspi, BIOS_WAIT_FOREVER);

/* Erase block, to which data has to be written */

if (Board_flashEraseBlk(boardHandle, blockNum))

{

SPI_log("\n Board_flashEraseBlk failed. \n");

testPassed = false;

break;

}

/* Generate the data */

GeneratePattern(txBuf, rxBuf, TEST_DATA_LEN);

/* Write buffer to flash */

if (Board_flashWrite(boardHandle, TEST_ADDR_OFFSET, txBuf,

TEST_DATA_LEN, (void *)(&ioMode)))

{

SPI_log("\n Board_flashWrite failed. \n");

testPassed = false;

break;

}

/* Reset receive buffer */

if (Board_flashRead(boardHandle, TEST_ADDR_OFFSET, rxBuf,

TEST_DATA_LEN, (void *)(&ioMode)))

{

SPI_log("\n Board_flashRead failed. \n");

testPassed = false;

break;

}

/* Verify Data */

if (VerifyData(txBuf, rxBuf, TEST_DATA_LEN) == false)

{

SPI_log("\n Data mismatch. \n");

testPassed = false;

break;

}

}

The semaphore, Qspi, is posted every second by a clock module. So, the loop is running every second. I have tried to run every 3 seconds and still got the same issue.

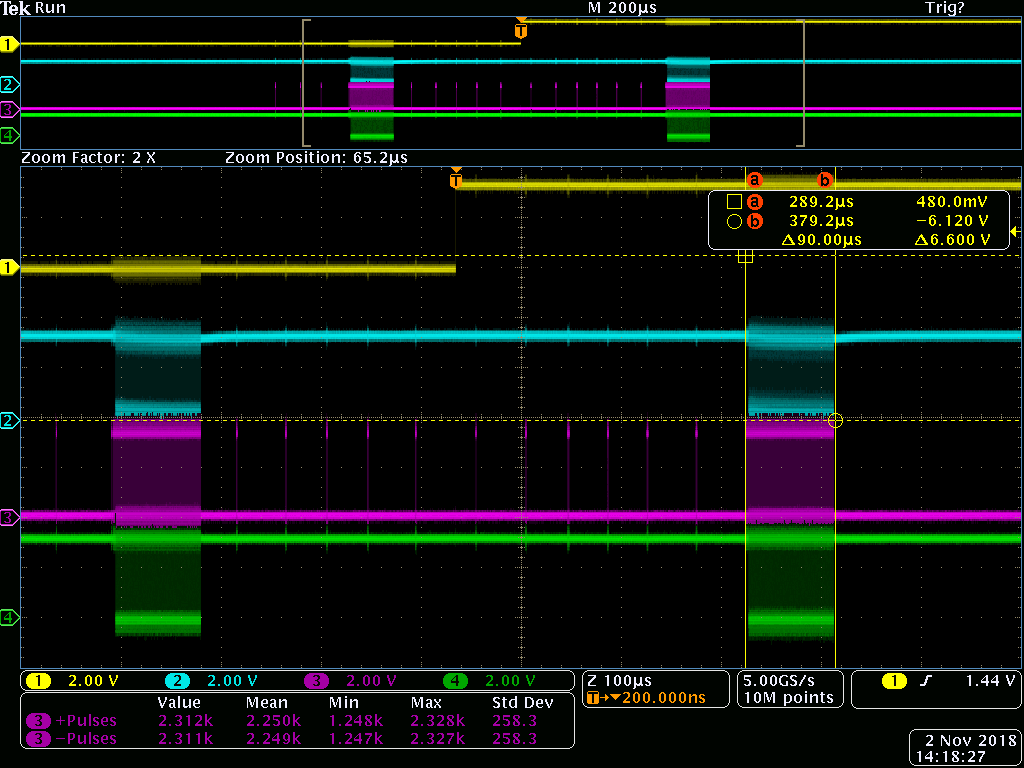

My test is always stalled in Board_flashRead API after several minutes testing. I insert code to toggle GPIO pins in several places to identify the place where the code is stalled.

and found it is waiting a word completion interrupt to post a semaphore forever.

In C:\ti\pdk_k2g_1_0_7\packages\ti\drv\spi\src\v0\QSPI_v0.clock

Line 884

if (object->qspiMode == QSPI_OPER_MODE_IND_XFER)

{

/* Only in indirect transfer mode, wait for the lock

posted form the word completion interrupt */

SPI_osalPendLock(object->transferComplete, SemaphoreP_WAIT_FOREVER);

}

The issue is gone if I change ioMode

from

ioMode = BOARD_FLASH_QSPI_IO_MODE_QUAD;

to

ioMode = BOARD_FLASH_QSPI_IO_MODE_SINGLE;

Q1: How is the word completion interrupt generated? How to identify it from probing QSPI signal lines?

Q2: Can the issue be resolves if I change SemaphoreP_WAIT_FOREVER to a limited time and recall Board_flashRead API if it returns error. I am not sure if I need to check/clean interrupts or additional stuff before call Board_flashRead again if it fails previously.

Thanks,

Brian