Dear sirs,

Recently, we have had an issue related with the invert_clockout flag belonging to the DDR controller of our AM437x.

We have our “custom” board with an AM4378 and a couple of DDR3 (MT41J128M16JT-125 IT) in fly-by topology running at 400MHz.

Now, we have assembled 52 boards and more than 20% of these have not passed the initial DDR3 tests, so, after completely dismiss an assembling problem we have checked the DDR3 controller registers.

In the initial parameters for our own board and till today we have used the invert_clockout = 0 as a recommendation of the TI GEL for the AM437x, but, by the other hand, these days we have realized that a new excel tool “SPRAC70_AM437x_EMIF_Configuration_Tool_V20”(April 2017) recommends using (for our system) invert_clockout = 1.

Initially in 2016, we characterized the uboot memory controller using the available excel tool at that moment: “AM43xx_DDR_register_calc_tool”(2015)

That tool let configure 4 registers and no more.

SDRAM_CONFIG - SDRAM_TIMING_1 - SDRAM_TIMING_2 and SDRAM_TIMING_3

For the rest of registers, we used the characteristics of the AM437x “GEL” for the Code Composer Studio available on the web: http://processors.wiki.ti.com/index.php/File:AM437x_GELs.zip

The code in the GEL “says” that if DDR_CK length >= DDR_DQS length then the clock is not inverted, else the other config must be used.

#define DDR3_PHY_CTRL 0x00008009 //enable h/w training

//invert_clkout=0 (if (DDR_CK length) >= (DDR_DQS length))

//disable half delay mode

//phy_dis_calib_rst set to 0

//RD_Latency = (CL + 2) - 1

//read latency of 7 for 400MHz

// hwlvmod RD_Latency = CL+3 ; 9 for 400MHz

// hwlvmod PHY_DLL_LOCK_DIFF incresed to 32- 0x00008xxx from 16 - 0x00004xxx

//#define DDR3_PHY_CTRL 0x00048009 //invert_clkout=1 (if (DDR_CK length) < (DDR_DQS length))

Then, due our DDR_CK length is larger than DDR_DQS length we used the option “invert_clockout = 0” to config the EMIF4D_DDR3_PHY_CTRL. Moreover to be coherent with the invert_clockout option, we also programmed the EMIF4D_EXT_PHY_CONTROL_1 according to the GEL

#define PHY_CTRL_SLAVE_RATIO 0x80 // if invert_clkout = 0

//#define PHY_CTRL_SLAVE_RATIO 0x100 // if invert_clkout = 1

WR_MEM_32(EXT_PHY_CTRL_1, (PHY_CTRL_SLAVE_RATIO<<20)|(PHY_CTRL_SLAVE_RATIO<<10)|(PHY_CTRL_SLAVE_RATIO<<0));

Now, the new tool “SPRAC70_AM437x_EMIF_Configuration_Tool_V20”(2017 april) contemplates many more parameters (type of DDR3, type of system and PCB layout) and really gives a lot of more registers. But despite the DDR_CK length in our board continues being larger than DDR_DQS length (the PCB has not changed), the tool says that for our board must have invert_clockout at 1 instead of 0.

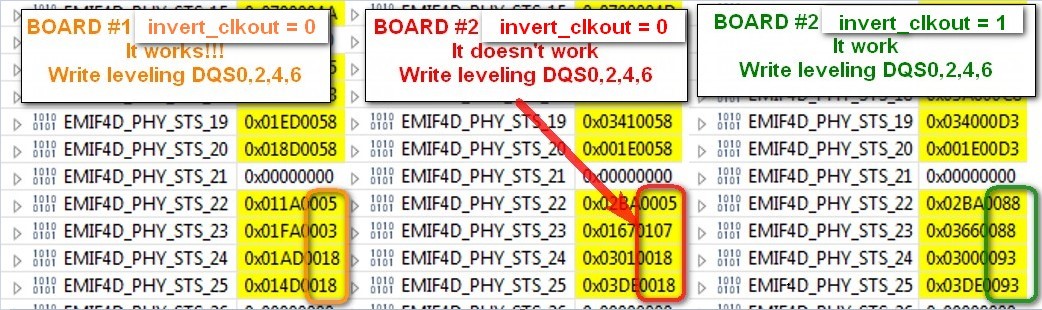

Really, with invert_clockout = 1 at both registers EMIF4D_DDR3_PHY_CTRL and EMIF4D_EXT_PHY_CONTROL_1 all our failing boards now functions.

Therefore, we are going to change our SW, but we have some questions:

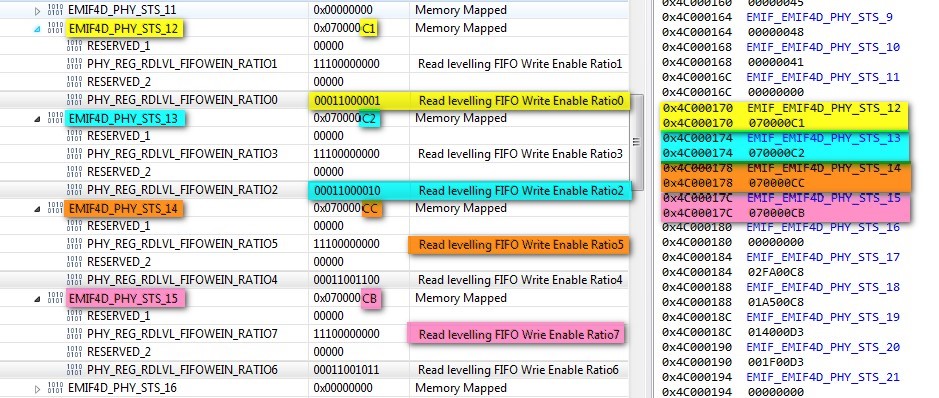

1) Is there some merit factor (as a registers) that can be polled to verify that hardware leveling is locked at the right point? There is the EMIF4D_PHY_STS_X collection but didn’t exist detailed documentation about what it means or how to interpret it.

2) It seems that the invert_clockout flag in EMIF4D_DDR_PHY_CTRL_1 is directly related with the value programmed in EMIF4D_EXT_PHY_CTRL_1, but there is no information about what this value means, except that this is the “ctrl slave ratio”(spruhl7d.pdf). I guess, this is like an initial seed for the convergence of DLL HWleveling algorithm, but it is supposition. We would like to have a detailed explanation about it.

3) Regarding to the necessity of the use of invert_clockout = 1 instead of invert_clockout = 0 in designs where DDR_CK length is larger than DDR_DQS length I would like you to confirm that it is a limitation of the granularity of the DDR3 DLL controller.

Although it is not explained, I guess that the AM4378 DDR3 hwleveling controller has a “granularity” or a minimum degrees (or picoseconds) correction capacity, in most of the cases, bigger than the (CK vs DQS) ps PCB difference to be corrected, and due to this minimum granularity, the AM4378 uses the “invert_clock” technics. I suppose that’s because, emitting the inverted clock from the AM4378 is like an emulation of a larger PCB skew between (CK vs DQS) just to exceed these minimum picoseconds granularity of the AM4378 DDR3 DLL controller. But it is only a supposition. Please confirm it.

4) Assuming that the values of our PCB are right introduced we would like if you were so kind to check it. We are going to launch the production and we don’t want new surprises.SPRAC70_AM437x_EMIF_Configuration_Tool_V20_modified_by_JFC.xlsx5807.2Gb_1_35V_DDR3L.pdf