Tool/software: Code Composer Studio

Hi

After successfully building the dgemm example found in linalg_1_2_0_0/examples/dsponly/dgemm_test via Makefile, The program built using the Makefile also successfully runs on the DSP and yields remarkable performance. However, I am experiencing different issues using CCS.

This is how I tried to build it from CCS:

1. I copy-pasted a project I previously created as described in "http://downloads.ti.com/mctools/esd/docs/openmp-dsp/building_openmp_app.html"

2. I copied dgemm_test.c, fc_config_c6678.c, ticblas_config.c and omp_config.cfg into my project folder

3. I added the necessary products via Project -> Properties.

4. If I build now, it throws the following error:

"/home/idris/ti/libarch_1_0_0_0/packages/ti/libarch/src/lib_cachecfg.h", line 38: fatal error #35: #error directive: "Unsupported OS! Please specify either LIB_OPENCL or LIB_RTOS"

I therefore add -DLIB_RTOS to the C6000 compiler flags under Project->Build->C6000 Compiler. This flag is also set when building via Makefile.

5. If I build now, I get:

"/home/idris/ti/libarch_1_0_0_0/packages/ti/libarch/src/lib_cachecfg.h", line 90: fatal error #35: #error directive: "Unsupported TARGET"

So I also add -DSOC_C6678, also passed in the Makefile.

6. It now finishes building but the Linker throws the following error:

undefined first referenced

symbol in file

--------- ----------------

cblas_dgemm ./dgemm_test.obj

lib_L1D_config_SRAM ./ticblas_config.obj

lib_get_L1D_SRAM_size ./ticblas_config.obj

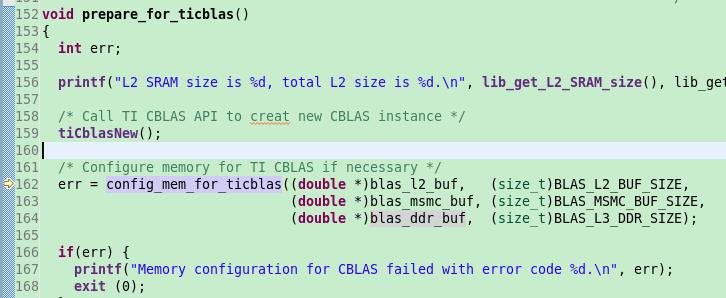

lib_get_L2_SRAM_size ./ticblas_config.obj

tiCblasDelete ./ticblas_config.obj

tiCblasGetSizes ./ticblas_config.obj

tiCblasInit ./ticblas_config.obj

tiCblasNew ./ticblas_config.obj

error #10234-D: unresolved symbols remain

And I unfortunately don't have any answer to this. Could maybe someone give me some hints on what I am doing wrong? Any help is appreciated. Please tell me if you need some additional information. Thank you very much.

Edit 1:

I was building in Debug Mode. However, changing to release did not help. Here the complete console output:

---------------------------------------------------------------------------------------

**** Build of configuration Release for project omp_linalglib4 **** /home/idris/ti/ccsv8/utils/bin/gmake -k -j 4 all -O Building file: "../dgemm_test.c" Invoking: C6000 Compiler "/home/idris/ti/ccsv8/tools/compiler/ti-cgt-c6000_8.2.4/bin/cl6x" -mv6600 -O2 --include_path="/home/idris/ti/openmp_dsp_c667x_2_06_02_01/packages/ti/runtime/openmp" --include_path="/home/idris/ti/openmp_dsp_c667x_2_06_02_01/packages/ti/runtime/openmp/platforms" --include_path="/home/idris/workspace_v8/omp_linalglib4" --include_path="/home/idris/ti/ccsv8/tools/compiler/ti-cgt-c6000_8.2.4/include" --define=LIB_RTOS --define=SOC_C6678 --diag_warning=225 --diag_wrap=off --display_error_number --openmp --preproc_with_compile --preproc_dependency="dgemm_test.d_raw" --cmd_file="configPkg/compiler.opt" "../dgemm_test.c" Finished building: "../dgemm_test.c" Building target: "omp_linalglib4.out" Invoking: C6000 Linker "/home/idris/ti/ccsv8/tools/compiler/ti-cgt-c6000_8.2.4/bin/cl6x" -mv6600 -O2 --define=LIB_RTOS --define=SOC_C6678 --diag_warning=225 --diag_wrap=off --display_error_number --openmp -z -m"omp_linalglib4.map" -i"/home/idris/ti/ccsv8/tools/compiler/ti-cgt-c6000_8.2.4/lib" -i"/home/idris/ti/ccsv8/tools/compiler/ti-cgt-c6000_8.2.4/include" --priority --reread_libs --diag_wrap=off --display_error_number --warn_sections --xml_link_info="omp_linalglib4_linkInfo.xml" --rom_model -o "omp_linalglib4.out" "./dgemm_test.obj" "./fc_config_c6678.obj" "./ticblas_config.obj" -l"configPkg/linker.cmd" -llibc.a <Linking> "configPkg/linker.cmd", line 131: warning #10068-D: no matching section warning #10247-D: creating output section ".tdata" without a SECTIONS specification warning #10247-D: creating output section ".tbss" without a SECTIONS specification undefined first referenced symbol in file --------- ---------------- cblas_dgemm ./dgemm_test.obj lib_L1D_config_SRAM ./ticblas_config.obj lib_get_L1D_SRAM_size ./ticblas_config.obj lib_get_L2_SRAM_size ./ticblas_config.obj tiCblasDelete ./ticblas_config.obj tiCblasGetSizes ./ticblas_config.obj tiCblasInit ./ticblas_config.obj tiCblasNew ./ticblas_config.obj error #10234-D: unresolved symbols remain error #10010: errors encountered during linking; "omp_linalglib4.out" not built gmake[1]: *** [omp_linalglib4.out] Error 1 >> Compilation failure makefile:140: recipe for target 'omp_linalglib4.out' failed gmake: *** [all] Error 2 makefile:136: recipe for target 'all' failed **** Build Finished ****

----------------------------------------------------------------

Edit 2:

Creating a makefile-project resolves the matter - still it would be amazing to find another solution.