產品編號: TDA2E

工具/軟件: Linux

Our own PCBA,

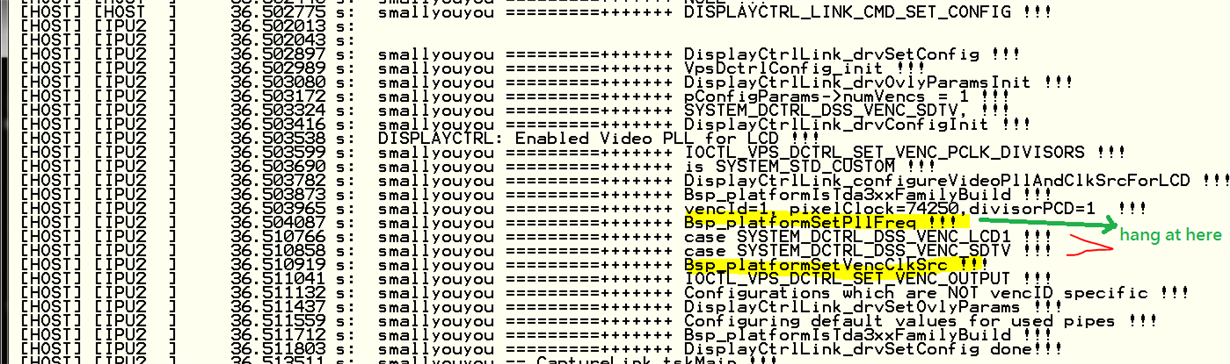

Some of them will hang on the Bsp_platformSetPllFreq function after executing app.out, but the other will run successfully.

We have two display modes, HDMI or LCD.

Both have a chance to fail.

I have tracked the code and added some logs, as shown below,

I also execute dss_clockdumps.sh to dump the information.

If I execute app.out fail,

and then I run dss_clockdumps.sh script,

it also hang, the log is as follows,

Also, after trying to annotate Bsp_platformSetPllFreq,

It becomes hang at Bsp_platformSetVencClkSrc.

If both are annotated,

It can execute app.out success, but the vedio will continue to move left and right

This is the dss part of my dts, as shown below,

below is my display config,

static Void ChainsCommon_SetDctrlConfig(

DisplayCtrlLink_ConfigParams *pPrm,

DisplayCtrlLink_OvlyParams *ovlyPrms,

DisplayCtrlLink_OvlyPipeParams *pipeOvlyPrms,

UInt32 displayType,

UInt32 displayWidth,

UInt32 displayHeight)

{

DisplayCtrlLink_VencInfo *pVInfo;

pPrm->numVencs = 1;

pPrm->tiedVencs = 0;

pVInfo = &pPrm->vencInfo[0];

pVInfo->tdmMode = DISPLAYCTRL_LINK_TDM_DISABLE;

if(displayType == CHAINS_DISPLAY_TYPE_LCD_7_INCH)

{

pPrm->deviceId = DISPLAYCTRL_LINK_USE_LCD;

pVInfo->vencId = SYSTEM_DCTRL_DSS_VENC_LCD1;

pVInfo->outputPort = SYSTEM_DCTRL_DSS_DPI1_OUTPUT;

pVInfo->vencOutputInfo.vsPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.hsPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

/* Below are of dont care for EVM LCD */

pVInfo->vencOutputInfo.fidPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.actVidPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->mInfo.standard = SYSTEM_STD_CUSTOM;

pVInfo->mInfo.width = displayWidth;

pVInfo->mInfo.height = displayHeight;

pVInfo->mInfo.scanFormat = SYSTEM_SF_PROGRESSIVE;

pVInfo->mInfo.pixelClock = 29232u;

pVInfo->mInfo.fps = 60U;

pVInfo->mInfo.hFrontPorch = 40u;

pVInfo->mInfo.hBackPorch = 40u;

pVInfo->mInfo.hSyncLen = 48u;

pVInfo->mInfo.vFrontPorch = 13u;

pVInfo->mInfo.vBackPorch = 29u;

pVInfo->mInfo.vSyncLen = 3u;

pVInfo->vencDivisorInfo.divisorLCD = 1;

pVInfo->vencDivisorInfo.divisorPCD = 4;

pVInfo->vencOutputInfo.dataFormat = SYSTEM_DF_RGB24_888;

pVInfo->vencOutputInfo.dvoFormat =

SYSTEM_DCTRL_DVOFMT_GENERIC_DISCSYNC;

pVInfo->vencOutputInfo.videoIfWidth = SYSTEM_VIFW_24BIT;

pVInfo->vencOutputInfo.pixelClkPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.aFmt = SYSTEM_DCTRL_A_OUTPUT_MAX;

/* Configure overlay params */

ovlyPrms->vencId = SYSTEM_DCTRL_DSS_VENC_LCD1;

}

else if(displayType == CHAINS_DISPLAY_TYPE_LCD_10_INCH)

{

pPrm->deviceId = DISPLAYCTRL_LINK_USE_LCD;

pVInfo->vencId = SYSTEM_DCTRL_DSS_VENC_LCD1;

pVInfo->outputPort = SYSTEM_DCTRL_DSS_DPI1_OUTPUT;

pVInfo->vencOutputInfo.vsPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.hsPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

/* Below are of dont care for EVM LCD */

pVInfo->vencOutputInfo.fidPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.actVidPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->mInfo.standard = SYSTEM_STD_CUSTOM;

pVInfo->mInfo.width = displayWidth;

pVInfo->mInfo.height = displayHeight;

pVInfo->mInfo.scanFormat = SYSTEM_SF_PROGRESSIVE;

/* pVInfo->mInfo.pixelClock = 74500U;

pVInfo->mInfo.fps = 60U;

pVInfo->mInfo.hBackPorch = 80U;

pVInfo->mInfo.hSyncLen = 62U;

pVInfo->mInfo.hFrontPorch = 48U;

pVInfo->mInfo.vBackPorch = 12U;

pVInfo->mInfo.vSyncLen = 35U;

pVInfo->mInfo.vFrontPorch = 6U;*/

pVInfo->mInfo.pixelClock = 74250U;

pVInfo->mInfo.fps = 60U;

pVInfo->mInfo.hBackPorch = 220U;

pVInfo->mInfo.hSyncLen = 40U;

pVInfo->mInfo.hFrontPorch = 110U;

pVInfo->mInfo.vBackPorch = 20U;

pVInfo->mInfo.vSyncLen = 5U;

pVInfo->mInfo.vFrontPorch = 5U;

pVInfo->vencDivisorInfo.divisorLCD = 1;

pVInfo->vencDivisorInfo.divisorPCD = 1;

pVInfo->vencOutputInfo.dataFormat = SYSTEM_DF_RGB24_888;

pVInfo->vencOutputInfo.dvoFormat =

SYSTEM_DCTRL_DVOFMT_GENERIC_DISCSYNC;

pVInfo->vencOutputInfo.videoIfWidth = SYSTEM_VIFW_24BIT;

pVInfo->vencOutputInfo.pixelClkPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.aFmt = SYSTEM_DCTRL_A_OUTPUT_MAX;

/* Configure overlay params */

ovlyPrms->vencId = SYSTEM_DCTRL_DSS_VENC_LCD1;

}

else if (displayType ==

CHAINS_DISPLAY_TYPE_LDC_10_INCH_LCDCTRL_TC358778_MIPI_DSI_1920_1200)

{

pPrm->deviceId = DISPLAYCTRL_LINK_USE_LCD;

pVInfo->vencId = SYSTEM_DCTRL_DSS_VENC_LCD1;

pVInfo->outputPort = SYSTEM_DCTRL_DSS_DPI1_OUTPUT;

pVInfo->vencOutputInfo.vsPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.hsPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

/* Below are of dont care for EVM LCD */

pVInfo->vencOutputInfo.fidPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.actVidPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->mInfo.standard = SYSTEM_STD_CUSTOM;

pVInfo->mInfo.width = displayWidth;

pVInfo->mInfo.height = displayHeight;

pVInfo->mInfo.scanFormat = SYSTEM_SF_PROGRESSIVE;

pVInfo->mInfo.pixelClock = 147000U;

pVInfo->mInfo.fps = 60U;

pVInfo->mInfo.hBackPorch = 32U;

pVInfo->mInfo.hSyncLen = 16U;

pVInfo->mInfo.hFrontPorch = 32U;

pVInfo->mInfo.vBackPorch = 16U;

pVInfo->mInfo.vSyncLen = 2U;

pVInfo->mInfo.vFrontPorch = 7U;

pVInfo->vencDivisorInfo.divisorLCD = 1;

pVInfo->vencDivisorInfo.divisorPCD = 1;

pVInfo->vencOutputInfo.dataFormat = SYSTEM_DF_RGB24_888;

pVInfo->vencOutputInfo.dvoFormat =

SYSTEM_DCTRL_DVOFMT_GENERIC_DISCSYNC;

pVInfo->vencOutputInfo.videoIfWidth = SYSTEM_VIFW_24BIT;

pVInfo->vencOutputInfo.pixelClkPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.aFmt = SYSTEM_DCTRL_A_OUTPUT_MAX;

/* Configure overlay params */

ovlyPrms->vencId = SYSTEM_DCTRL_DSS_VENC_LCD1;

}

else if(displayType == CHAINS_DISPLAY_TYPE_HDMI_720P

|| displayType == CHAINS_DISPLAY_TYPE_HDMI_1080P)

{

pPrm->deviceId = DISPLAYCTRL_LINK_USE_HDMI;

pVInfo->vencId = SYSTEM_DCTRL_DSS_VENC_HDMI;

pVInfo->outputPort = SYSTEM_DCTRL_DSS_HDMI_OUTPUT;

pVInfo->vencOutputInfo.vsPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.hsPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

/* Below are of dont care for EVM LCD */

pVInfo->vencOutputInfo.fidPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.actVidPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.dataFormat = SYSTEM_DF_RGB24_888;

pVInfo->vencOutputInfo.dvoFormat =

SYSTEM_DCTRL_DVOFMT_GENERIC_DISCSYNC;

pVInfo->vencOutputInfo.videoIfWidth = SYSTEM_VIFW_24BIT;

pVInfo->vencOutputInfo.pixelClkPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.aFmt = SYSTEM_DCTRL_A_OUTPUT_MAX;

/* Configure overlay params */

ovlyPrms->vencId = pVInfo->vencId;

}

else if(displayType == CHAINS_DISPLAY_TYPE_FPD)

{

pPrm->deviceId = DISPLAYCTRL_LINK_USE_LCD;

pVInfo->vencId = SYSTEM_DCTRL_DSS_VENC_LCD3;

pVInfo->outputPort = SYSTEM_DCTRL_DSS_DPI3_OUTPUT;

pVInfo->mInfo.width = displayWidth;

pVInfo->mInfo.height = displayHeight;

pVInfo->mInfo.pixelClock = 74250;

pVInfo->mInfo.fps = 60U;

pVInfo->mInfo.hBackPorch = 148U;

pVInfo->mInfo.hSyncLen = 44U;

pVInfo->mInfo.hFrontPorch = 88U;

pVInfo->mInfo.vBackPorch = 15U;

pVInfo->mInfo.vSyncLen = 5U;

pVInfo->mInfo.vFrontPorch = 2U;

pVInfo->vencDivisorInfo.divisorLCD = 1;

pVInfo->vencDivisorInfo.divisorPCD = 1;

pVInfo->vencOutputInfo.vsPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.hsPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

/* Below are of dont care for EVM LCD */

pVInfo->vencOutputInfo.fidPolarity = SYSTEM_DCTRL_POLARITY_ACT_LOW;

pVInfo->vencOutputInfo.actVidPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.dataFormat = SYSTEM_DF_RGB24_888;

pVInfo->vencOutputInfo.dvoFormat =

SYSTEM_DCTRL_DVOFMT_GENERIC_DISCSYNC;

pVInfo->vencOutputInfo.videoIfWidth = SYSTEM_VIFW_24BIT;

pVInfo->vencOutputInfo.pixelClkPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.aFmt = SYSTEM_DCTRL_A_OUTPUT_MAX;

/* Configure overlay params */

ovlyPrms->vencId = pVInfo->vencId;

}

else

{

OSA_assert(0);

}

if(displayType == CHAINS_DISPLAY_TYPE_HDMI_720P)

{

pVInfo->mInfo.standard = SYSTEM_STD_720P_60;

}

else if (displayType == CHAINS_DISPLAY_TYPE_HDMI_1080P)

{

pVInfo->mInfo.standard = SYSTEM_STD_1080P_60;

}

else if (displayType == CHAINS_DISPLAY_TYPE_FPD)

{

pVInfo->mInfo.standard = SYSTEM_STD_720P_60;

}

/* TODO Dont know what to set here */

pVInfo->mode = 0;

pVInfo->isInputPipeConnected[0] =

TRUE;

pVInfo->isInputPipeConnected[1] =

TRUE;

pVInfo->isInputPipeConnected[2] =

TRUE;

pVInfo->isInputPipeConnected[3] =

TRUE;

pVInfo->writeBackEnabledFlag = FALSE;

/* Setting other overlay parameters common to both Venc */

ovlyPrms->deltaLinesPerPanel = 0;

ovlyPrms->alphaBlenderEnable = 0;

ovlyPrms->backGroundColor = 0x10;

ovlyPrms->colorKeyEnable = 1;

ovlyPrms->colorKeySel = SYSTEM_DSS_DISPC_TRANS_COLOR_KEY_SRC;

ovlyPrms->ovlyOptimization = SYSTEM_DSS_DISPC_OVLY_FETCH_ALLDATA;

ovlyPrms->transColorKey = DRAW2D_TRANSPARENT_COLOR;

/* Setting overlay pipe parameters */

pipeOvlyPrms[0].pipeLine = SYSTEM_DSS_DISPC_PIPE_VID1;

pipeOvlyPrms[0].globalAlpha = 0xFF;

pipeOvlyPrms[0].preMultiplyAlpha = 0;

pipeOvlyPrms[0].zorderEnable = TRUE;

pipeOvlyPrms[0].zorder = SYSTEM_DSS_DISPC_ZORDER0;

pipeOvlyPrms[1].pipeLine = SYSTEM_DSS_DISPC_PIPE_VID2;

pipeOvlyPrms[1].globalAlpha = 0xFF;

pipeOvlyPrms[1].preMultiplyAlpha = 0;

pipeOvlyPrms[1].zorderEnable = TRUE;

pipeOvlyPrms[1].zorder = SYSTEM_DSS_DISPC_ZORDER1;

pipeOvlyPrms[2].pipeLine = SYSTEM_DSS_DISPC_PIPE_VID3;

pipeOvlyPrms[2].globalAlpha = 0xFF;

pipeOvlyPrms[2].preMultiplyAlpha = 0;

pipeOvlyPrms[2].zorderEnable = TRUE;

pipeOvlyPrms[2].zorder = SYSTEM_DSS_DISPC_ZORDER2;

pipeOvlyPrms[3].pipeLine = SYSTEM_DSS_DISPC_PIPE_GFX1;

pipeOvlyPrms[3].globalAlpha = 0xFF;

pipeOvlyPrms[3].preMultiplyAlpha = 0;

pipeOvlyPrms[3].zorderEnable = TRUE;

pipeOvlyPrms[3].zorder = SYSTEM_DSS_DISPC_ZORDER3;

}

Can someone see if there are any problems?

My environment is tda2eg and visionsdk_3.02