Hello TI Experts,

I studied a few notes on the DDR3 memory layout from TI (SPRABI1C), NXP, Micron, Xilinx, and other manufacturers, and I had some questions:

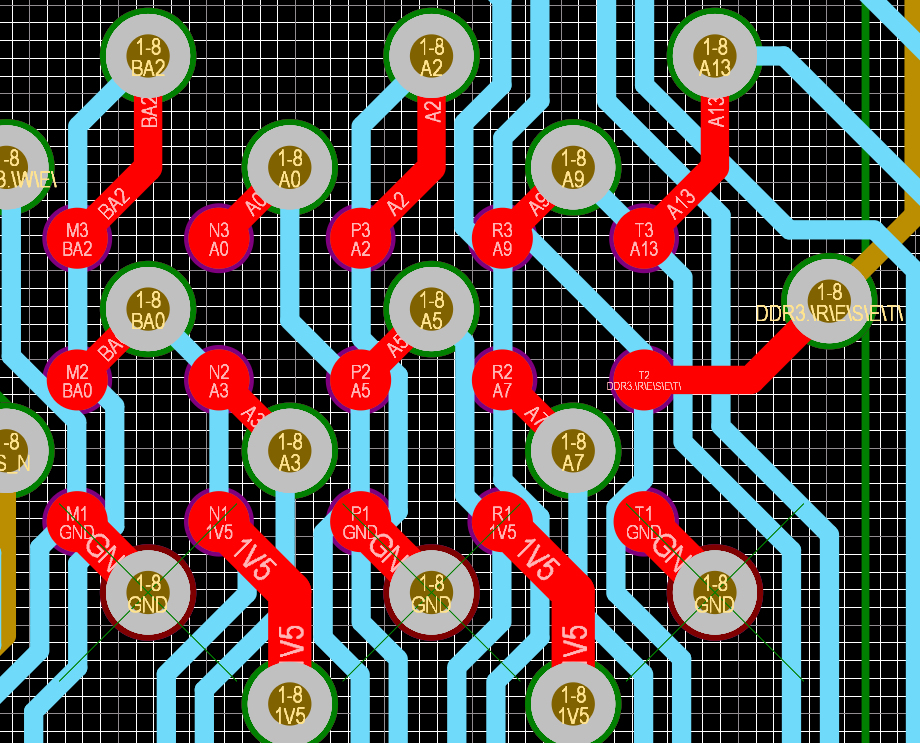

1. To which signal group does the DDR3.RESET signal (T2 pin in FBGA-96) belong to ADDR / COMMAND or CONTROL and is it necessary to match the length of this signal according to the length of the signals in one of these two groups or is it completely independent of the groups and length alignment?

2. Everywhere it is said that the length of the clock signals of the differential pair CK_P & CK_N should be 5 mil longer than the maximum length of the data bank signals?

For example, take one memory module with two banks BANK0 and BANK1:

BANK0 - length matching in group (difference 20 mil) - max.length for all signals in group is = 17.04mm

BANK1 - length matching in group (difference 20 mil) - max.length for all signals in group is = 31.84mm

Question:

What should be the length of the minimum length of the differential pair CK_P & CK_N?

Answer:

The minimum length of the differential pair is CK_P & CK_N = 32.34mm (maximum data signals length of banks (31.84mm) + 5mil).

Are my calculations and guesses correct?

3. My design program (Altium), when adding an impedance calculation profile, uses several reference planes (# 2 and # 4) for conductors (# 3) located on the inner layers of the board.

===========================

# 2 Ground Plane - Inner Layer

===========================

# 3 High Frequency - Inner Layer

===========================

# 4 Power Plane - Inner Layer

===========================

Questions:

a. Is it true that the supporting plane is always the same? (either above or below)

b. Will the split plane of the plane on the layer (# 4) affect the layer with conductors (# 3) if I choose the plane (# 2) as the only reference plane based on our communication in this topic? Or will both planes have an impact?