Hi, I've been working on a C6672 DSP and trying to find a way to boot it with an application image for months now. I'm able to download and debug applications on both cores using the XDS560 emulator, but still hardly have any idea on how the bootloading process is supposed to work.

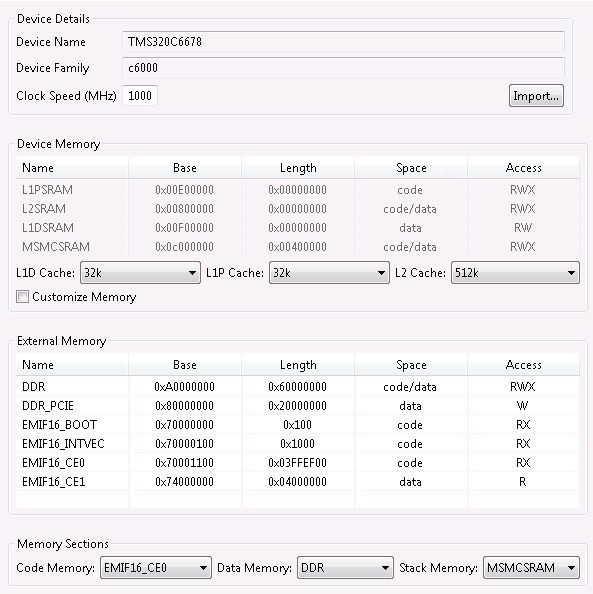

I have a 128-MB NOR flash connected to the DSP through the EMIF16 interface (in the address range 0x7000000:0x77FFFFFF), and I want to convert my application.out file to a bootable *.bin file so that the DSP autonomously boots with that application image flashed onto NOR.

I've referred to the following wiki pages and forum posts:

https://e2e.ti.com/support/processors/f/791/t/367102

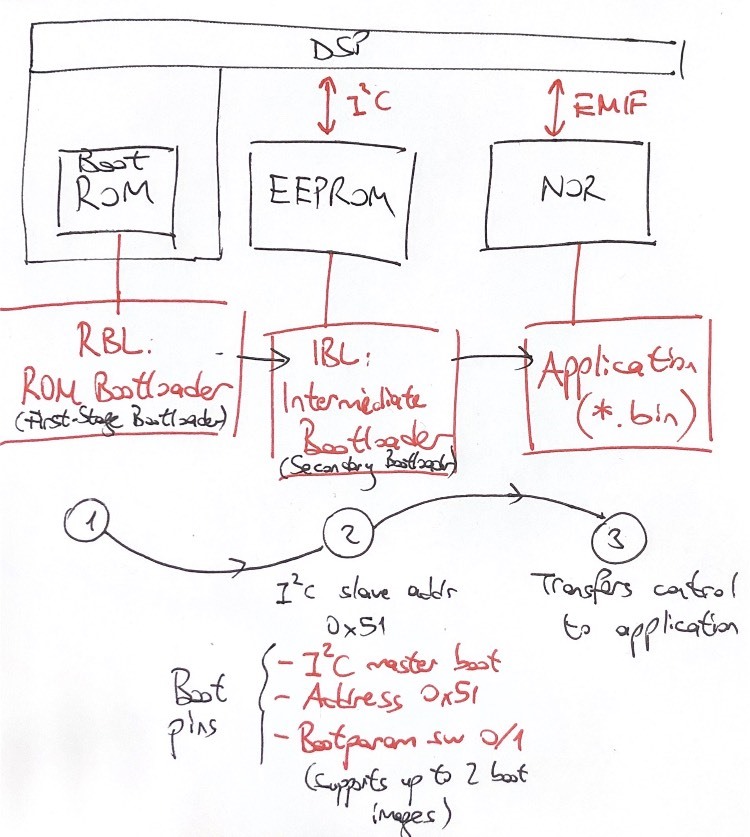

To my understanding, the bootloading process works as follows (please verify my in case I'm mistaken):

- The DSP has an internal boot ROM (at 0x20B00000:0x20B1FFFF) consisting of the ROM Bootloader (RBL).

- When reset, DSP uses the RBL (regardless of the boot pins), and then, the RBL checks the boot pins and transfers control to the Intermediate Bootloader (IBL), which is located on the EEPROM connected via I2C (on slave address 0x51).

- The IBL then finds the bootable *.bin file on the NOR flash and transfers it the control over the processor.

What's confusing to me is:

- Given the boot pins are set to I2C master boot with slave address 0x51, how does the IBL know where the application image is located? I mean, in this example, the IBL transfers control to the application binary located in the NOR flash, but how does it know the application is in NOR flash and in which address range the application is flashed?

- This BIN image is generated using the tools hex6x, b2ccs, and ccs2bin on the built OUT file, isn't it? So how should I populate the RMD file when using hex6x? Is the RMD example in https://e2e.ti.com/support/processors/f/791/t/367102 still valid here?

Thanks in advance,

Best regards.