Other Parts Discussed in Thread: SYSCONFIG

Hi,

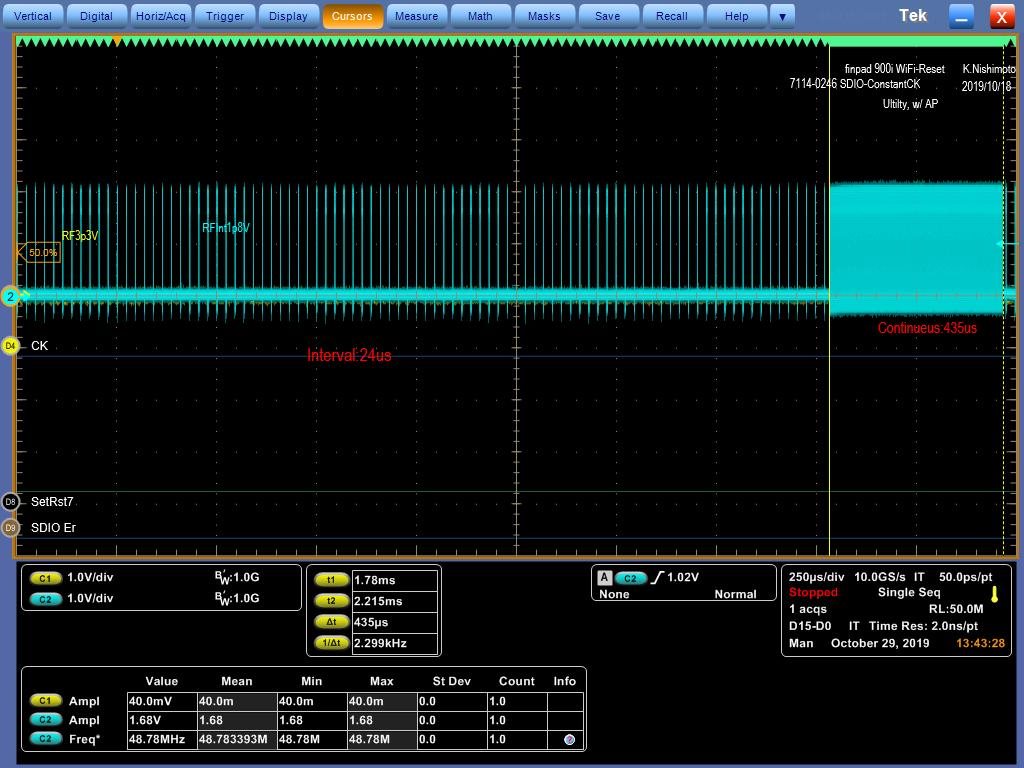

We need to change SDIO clock action from intermittent to conrinuous. I understood setting the EXTFREE bit of MMCHS_CON register.

However, we change the bit and our system occuer kernel panic.(below error message)

We try only to read the register but the erroe occur as well.

We wonder that we need to any steps to access or view the register.

So do you have any advice?

【error message】

Kernel panic not syncing: Atempted to kill init!

I have already checked https://e2e.ti.com/support/processors/f/791/t/702537?tisearch=e2e-sitesearch&keymatch=SDIO%252525252520clock%252525252520continuous.