Other Parts Discussed in Thread: TMDSSK3358

HI

I have one question for DDR3 DQ[0:15] Design

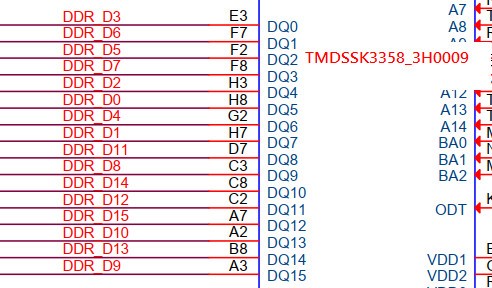

1. The Demo Schematic "TMDSSK3358_3H0009_REV1_2B_SCH" for DDR3 Design , figure as below .

(AM335X) DDR_D3 point to the DDR3 DQ0 , DDR_D6 point to the DQ1 , etc .i think this is for layout issue so can doing signal change , is right ?

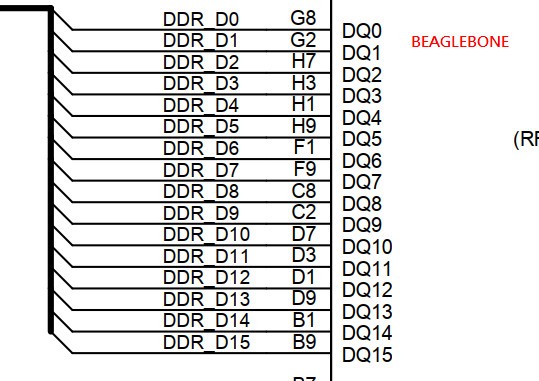

2. if DDR3 of TMDSSK3358_3H0009DDR3 Demo Board change to DDR3L ,the signal( DQ[0:15]) can be change ?

Thanks'