Hi All,

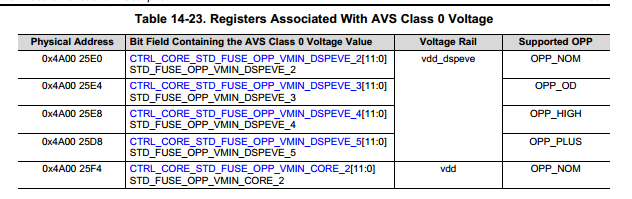

We have an ambiguity in the datasheet, TI header and Memory Map view of HW registers for AVS on TDA3

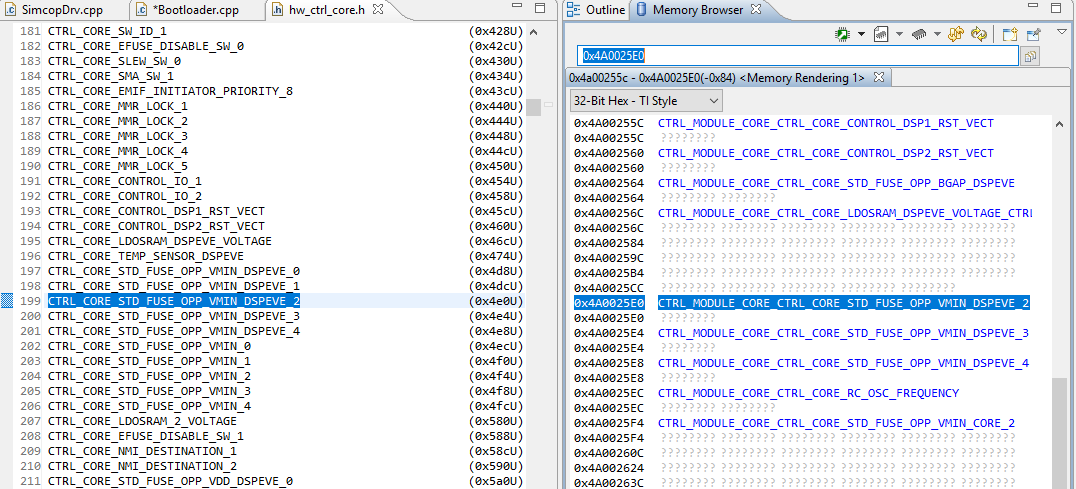

In TI header file #include "hw_ctrl_core.h", we have the register name as mentioned in the datasheet

#define CTRL_CORE_STD_FUSE_OPP_VMIN_DSPEVE_2 (0x4e0U) but the offset is different.

The memory map view shows a different register name altogether with the same physical address as mentioned in datasheet.

CTRL_MODULE_CORE_CTRL_CORE_STD_FUSE_OPP_VMIN_DSPEVE_2 = 0x420025E0;

The same is for all the other registers.

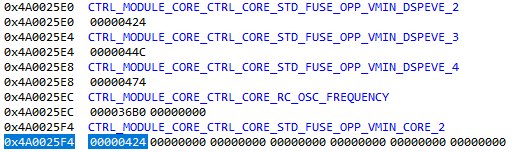

So should we read the registers with memory address from the memory map view of the TDA3 HW

CTRL_MODULE_CORE_CTRL_CORE_STD_FUSE_OPP_VMIN_DSPEVE_2 = 0x420025E0; and

CTRL_MODULE_CORE_CTRL_CORE_STD_FUSE_OPP_VMIN_CORE_2 = 0x420025F4;

Values Read from these registers

Thanks