Hi,

I previously posted questions about DDR2 measurements which were not okay. We have updated the design to solve the non conformance's. Now I do still see some strange behavior in our signals and was wondering if this is normal behavior or maybe a board or setting problem. (We are running at 266 MHz).

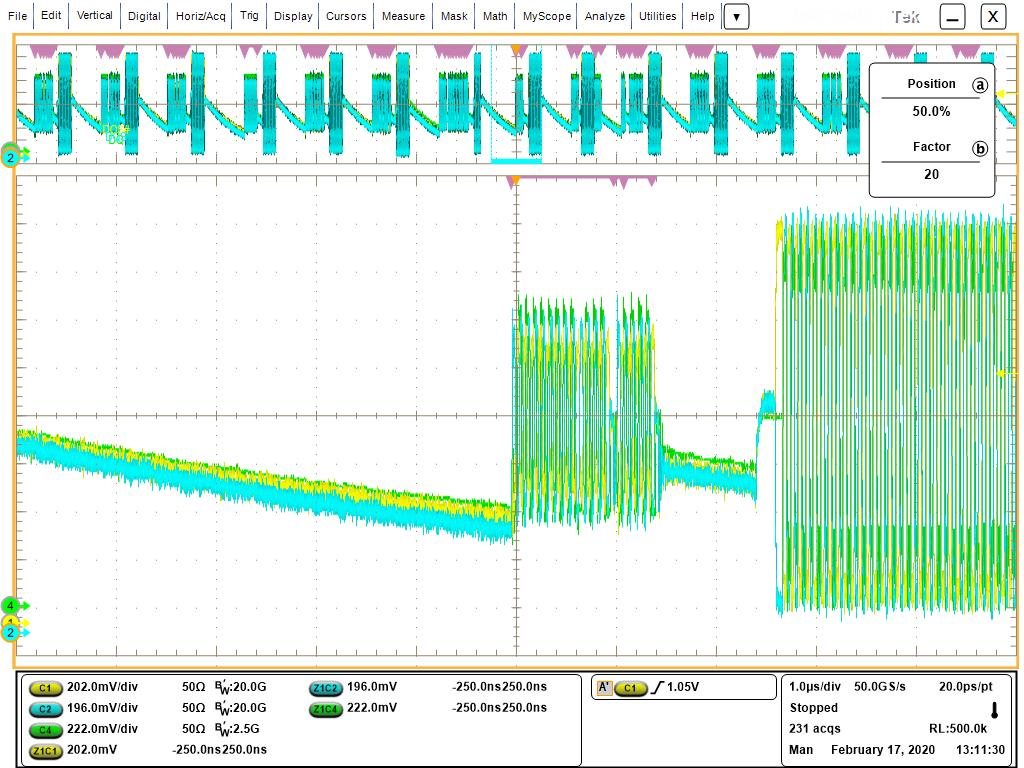

When writing to the memory the signals are looking like this:

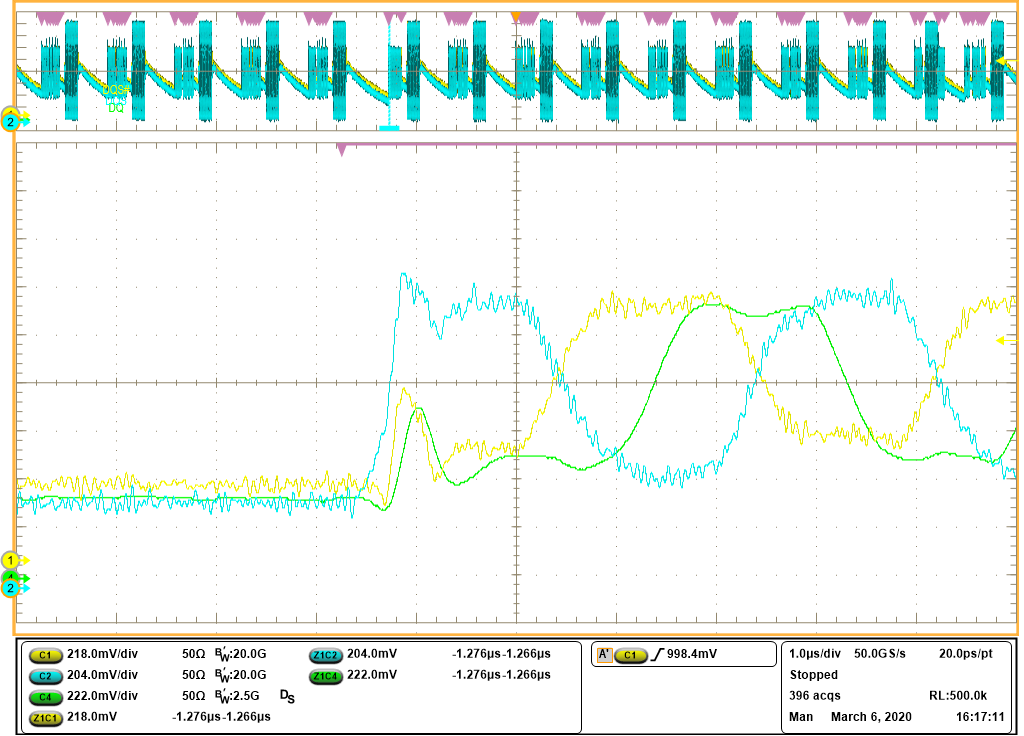

and zoomed in:

The signals are measured at the DDR2 device:

S1 (Yellow) -> DQS1_n

S2 (Blue) -> DQS1_p

S4 (Green) -> DQ10

IO_CTRL_x = 0x0000030B

In the last picture where the DQS starts, a glitch or pulse is visible. Is this normal behavior of the signals? And can you give a statement about how the signals are looking?

Please let me know if you need more information. Thank you!

Regards,

F. Veger