Hi,

Customer board can't link with PCIe 5GT/s. It happens in their application that connecting AM5746(EP)---AM5746(RC).

Customer checked PCIECTRL_TI_CONF_DEVICE_CMD (0x51002104) register because find the cause.

RC's register change was confirmed.

PCIECTRL_TI_CONF_DEVICE_CMD

NG

0x0000 0000

0x0000 0009

0x0000 000D

0x0000 0000

OK

0x0000 0000

0x0000 0009

0x0000 000D

0x0000 0045

EP's

NG: 0x0000 0000 -> 0000 0000

OK: 0x0000 0000 -> 0000 0045

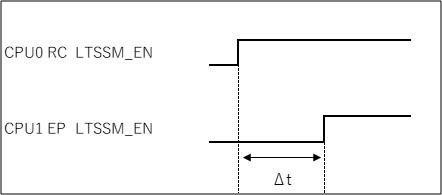

They checked PDK driver, but they didn't find any processing that set LTSSM_EN Field to 1.

We assume that HW set this field to 0.

Question 1:

Is LTSSM_EN set to 0 due to external factors?

Question 2:

Would you tell me how to retry if link fail (=LTSSM_EN:0)?

Customer's board

bios_6_76_00_08

pdk_am57xx_1_0_11

Regards,

Rei