Other Parts Discussed in Thread: SYSBIOS

Hi experts:

issues:

NULLSRC-2: No emptyQue is observed and the video is not good:

[IPU1-0] 217.960714 s: NULLSRC-2: No emptyQue, frameId-2254, chId-0

i can observed Declink_h264DecodeFrame takes more 40ms in sometime when decode with 720p@25fps.

what did i do to find the issue:

tm1 = Utils_getCurGlobalTimeInUsec();

fxns->algActivate((IALG_Handle) handle);

error = handle->fxns->ividdec3.process((IVIDDEC3_Handle) handle,

inputBufDesc,

outputBufDesc,

(IVIDDEC3_InArgs *) inArgs,

(IVIDDEC3_OutArgs *) outArgs);

fxns->algDeactivate((IALG_Handle) handle);

tm1 = Utils_getCurGlobalTimeInUsec() - tm1;

if (tm1 > (10 * 1000))

{

Vps_printf("ividdec3 fid=%d tm %lld ***** \n", pReqObj->InBuf->frameId, tm1);

}

log:

[HOST] [IPU1-0] 272.541603 s: ividdec3 fid=3051 tm 12872 error!!!! *****

[HOST] [IPU1-0] 272.602055 s: ividdec3 fid=3052 tm 28549 error!!!! *****

[HOST] [IPU1-0] 272.638443 s: ividdec3 fid=3053 tm 15067 error!!!! *****

[HOST] [IPU1-0] 272.830354 s: ividdec3 fid=3055 tm 45233 error!!!! *****

[HOST] [IPU1-0] 272.883822 s: ividdec3 fid=3056 tm 11315 *****

[HOST] [IPU1-0] 272.911517 s: ividdec3 fid=3057 tm 13207 *****

[HOST] [IPU1-0] 272.980814 s: ividdec3 fid=3058 tm 19703 *****

[HOST] [IPU1-0] 273.131977 s: ividdec3 fid=3059 tm 119899 *****

environment:

the decode version is h264vdec_02_00_17_01_production

vision sdk 3.2

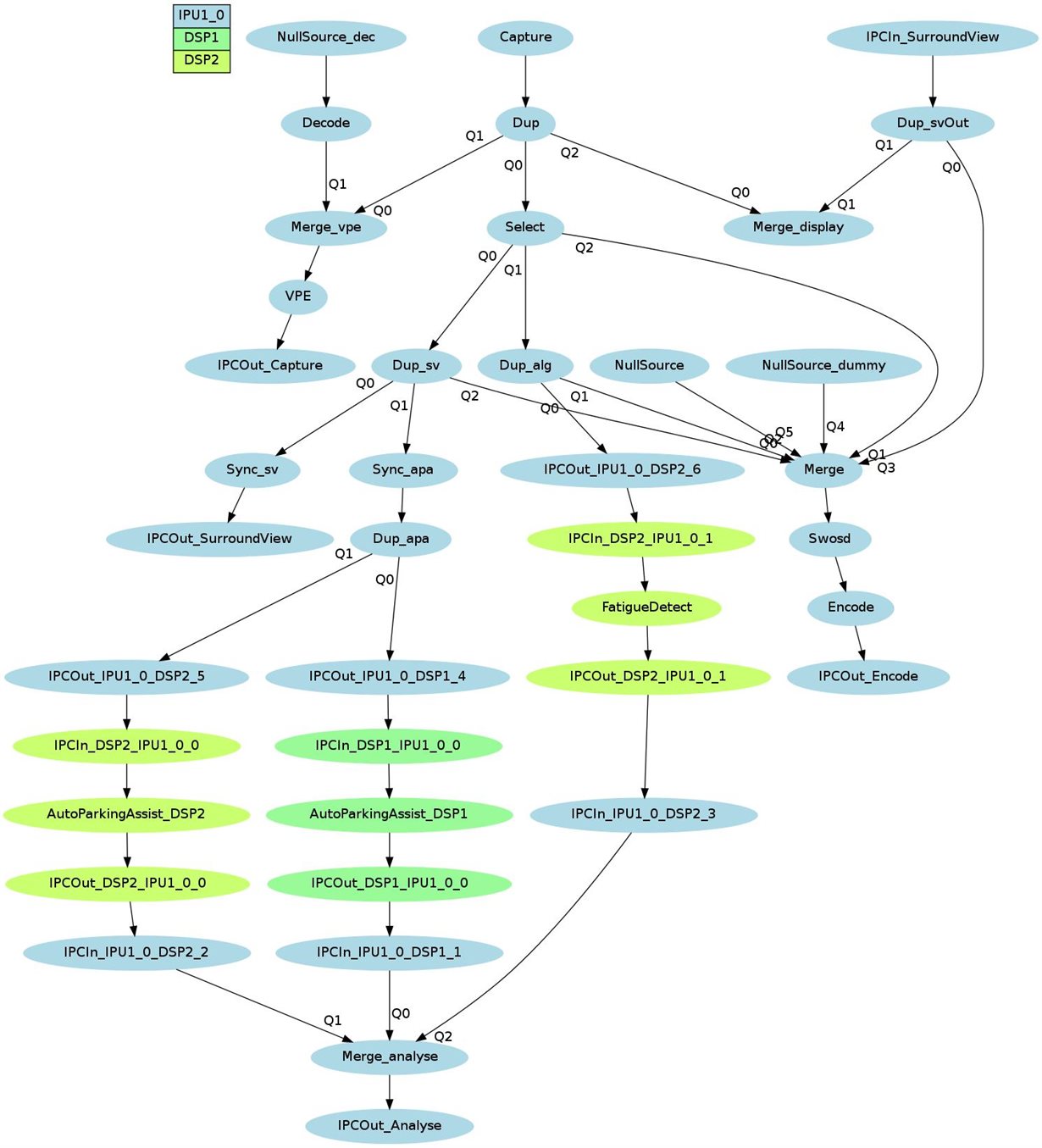

our usecase in IPU1:

7-channel capture of 720p

our usecase in a15:

take 4 yuv frm from ipcout_surroundView to do video fusion though GPU.

take 1 yuv frm from ipcout_capture to do fd though arm cpu.

our EMIF test result:

M4 statCollector:

SCI_EMIF1 RD+WR maximum:2374.584718

SCI_EMIF2 RD+WR maximum:3109.538576

attachment for the detail result:

Statistics Collector,

STATISTIC Avg Data Peak Data

COLLECTOR MB/s MB/s

--------------------------------------------------

SCI_EMIF1 RD+WR | 1175.080023 2374.584718

SCI_EMIF2 RD+WR | 1444.636093 3109.538576

SCI_EMIF1 RD ONLY | 814.471451 1525.882800

SCI_EMIF1 WR ONLY | 360.761496 878.057164

SCI_EMIF2 RD ONLY | 1081.784603 2234.331402

SCI_EMIF2 WR ONLY | 363.088525 912.946885

SCI_MA_MPU_P1 | 104.285875 567.077803

SCI_MA_MPU_P2 | 220.883907 1117.839188

SCI_DSS | 428.426779 473.662801

SCI_IPU1 | 34.330070 53.968017

SCI_VIP1_P1 | 29.553571 38.795876

SCI_VIP1_P2 | 64.905693 75.743583

SCI_VPE_P1 | 115.062491 339.556288

SCI_VPE_P2 | 115.070836 339.609072

SCI_DSP1_MDMA | 257.788436 467.796699

SCI_DSP1_EDMA | 0.000000 0.000000

SCI_DSP2_MDMA | 254.011228 439.289042

SCI_DSP2_EDMA | 0.000000 0.000000

SCI_EVE1_TC0 | 0.000000 0.000000

SCI_EVE1_TC1 | 0.000000 0.000000

SCI_EVE2_TC0 | 0.000000 0.000000

SCI_EVE2_TC1 | 0.000000 0.000000

SCI_EDMA_TC0_RD | 0.005387 0.060739

SCI_EDMA_TC0_WR | 0.005387 0.060739

SCI_EDMA_TC1_RD | 0.022858 0.185149

SCI_EDMA_TC1_WR | 0.045729 0.370298

SCI_VIP2_P1 | 8.796014 17.754530

SCI_VIP2_P2 | 20.510495 41.427237

SCI_VIP3_P1 | 17.917204 35.509060

SCI_VIP3_P2 | 40.548533 82.854474

SCI_EVE3_TC0 | 0.000000 0.000000

SCI_EVE3_TC1 | 0.000000 0.000000

SCI_EVE4_TC0 | 0.000000 0.000000

SCI_EVE4_TC1 | 0.000000 0.000000

SCI_IVA | 107.746195 650.960122

SCI_GPU_P1 | 523.765875 957.638688

SCI_GPU_P2 | 531.234214 948.841269

SCI_GMAC_SW | 0.000000 0.000000

SCI_OCMC_RAM1 | 0.000000 0.000000

SCI_OCMC_RAM2 | 0.000000 0.000000

SCI_OCMC_RAM3 | 0.000000 0.000000

Performance from document:

i read from DRA74x_75x and DRA72x Performance(SPRAC46A)

|

Interleaved (Two 32-Bit Memory) |

||

|

EMIF1 |

EMIF2 |

|

|

3650.88 |

3642.88 |

|

clock of our hardware setup:

533Mhz each EMIF interface.

EMIF1 has 2*256MiB chips connected.

EMIF2 has 2*512MiB chip connected.

EMIF has ecc chip connected.

attach for DMM_LISA_MAP_i in case you want to know if they are interleaved.

~ # omapconf read 0x4E000040

00000000

~ # omapconf read 0x4E000044

80640300

~ # omapconf read 0x4E000048

C0500220

~ # omapconf read 0x4E00004c

FF020100

formula for emif payload:

Interleave: 32bits * 1066MHz * 2-interleave * 0.65(actual rate) / 8 = 5,543.2MB/s

Non-interleave: 5,543.2MB/s / 2 = 2,771.6MB/s

which is that far to the test result.

please tell me if it's over run or not.

any suggestion will be appreciated.