Hello team,

Our customer is developing system board with TMS320C6457, customer encountered the problem which was related to POR.

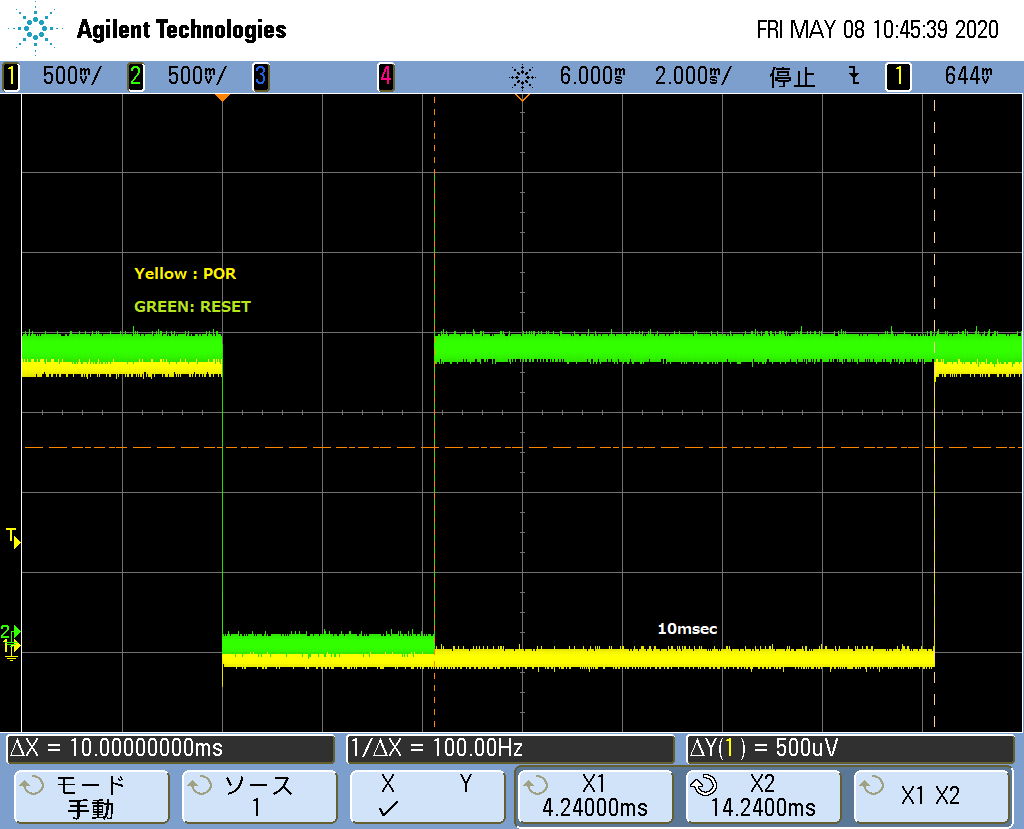

This board is working fine after system power-up, however, when POR was executed after system power-up, system seems freeze as follows (Power is keeping to supply). Although I requested customer to capture RESETSTAT in addition, RESETSTAT terminal was implemented as N.C, unfortunately. Customer is using EMIFABoot mode.

As far s I checked datasheet[7.6.1 Power-on Reset], it seems, device power-up cycle is not required to initiate a power-on reset.Is there any limitation for POR execution? If customer wants to do system-reset, should they initiate “Warm Reset”?

It will be appreciated if you will be share Expert’s advice/comments on this.

Best regards,

Miyazaki