Hi,

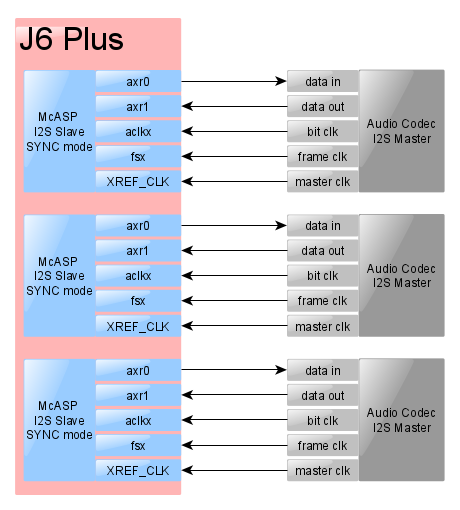

I have a question about the Jacinto McASP that I cannot resolve clearly. We currently have 3 devices connected to our Jacinto through 3 different McASPs. These 3 McASPs act as slaves in the I2S communication and are configured in SYNC mode. The McASP pins are configured as follows:

- two data lines, one input and one output.

- input bit clock

- input frame clock

- input master clock

The figure below tries to be an idea of our configuration:

My doubt is about the input master clock:

- it is really necessary in this case? As far as I understand, no, but I'm not sure.

- If not, could you tell us in which cases, being the McASP configured as slave, could the master clock be useful? For the only case I can think of is when the McASP is a teacher.

- if yes, Is the connection to the XREF OK? Since the AHCLKX is only output, I guess you have to use the XREF, right?

Regards,