Other Parts Discussed in Thread: LM10011

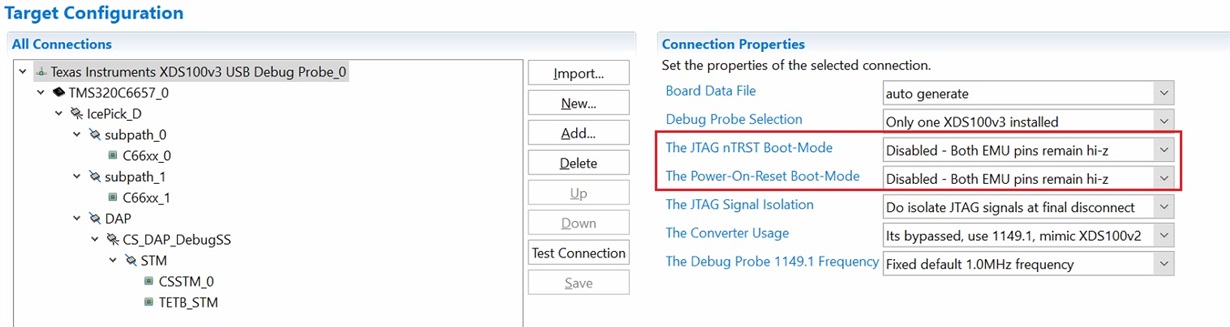

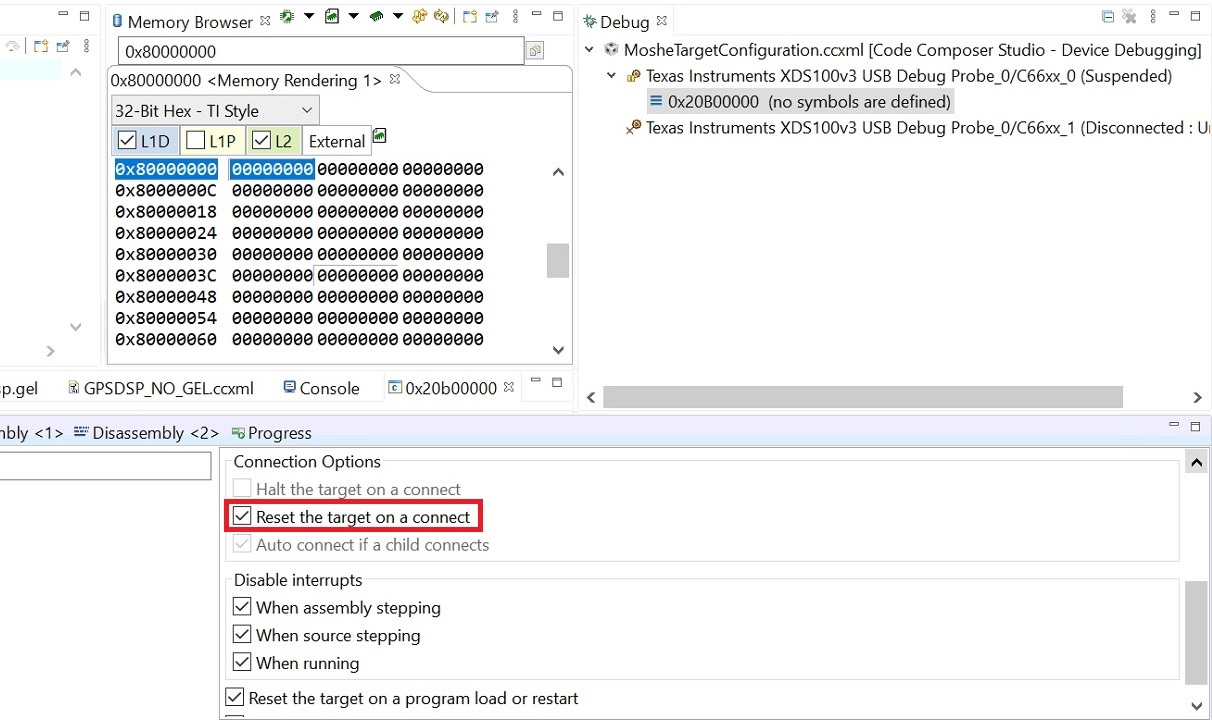

I have a custom board with C6657 and XDS100v2 JTAG emulator.

The "test connection" for the JTAG passes,

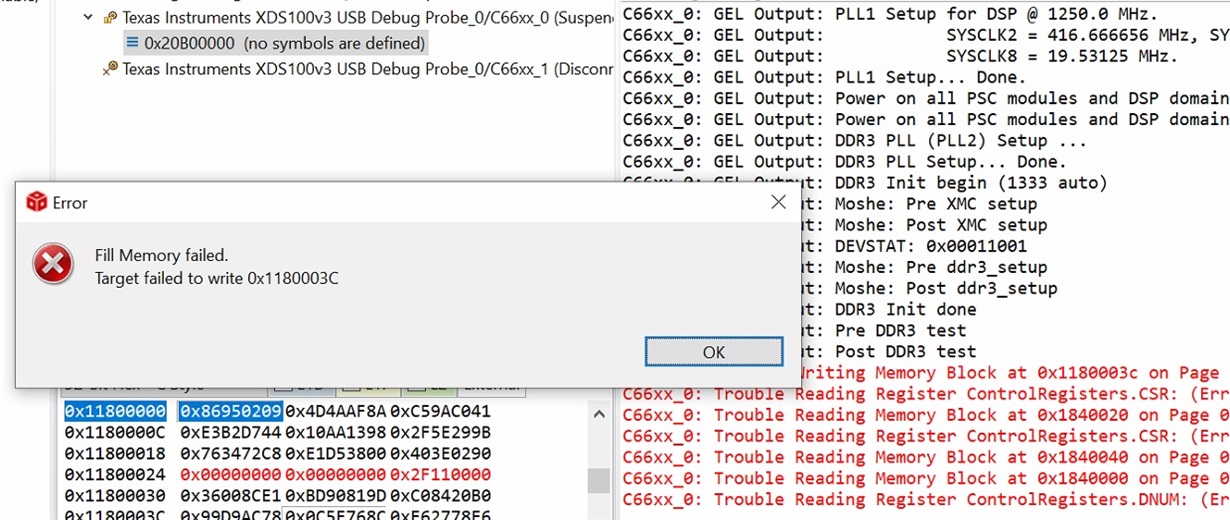

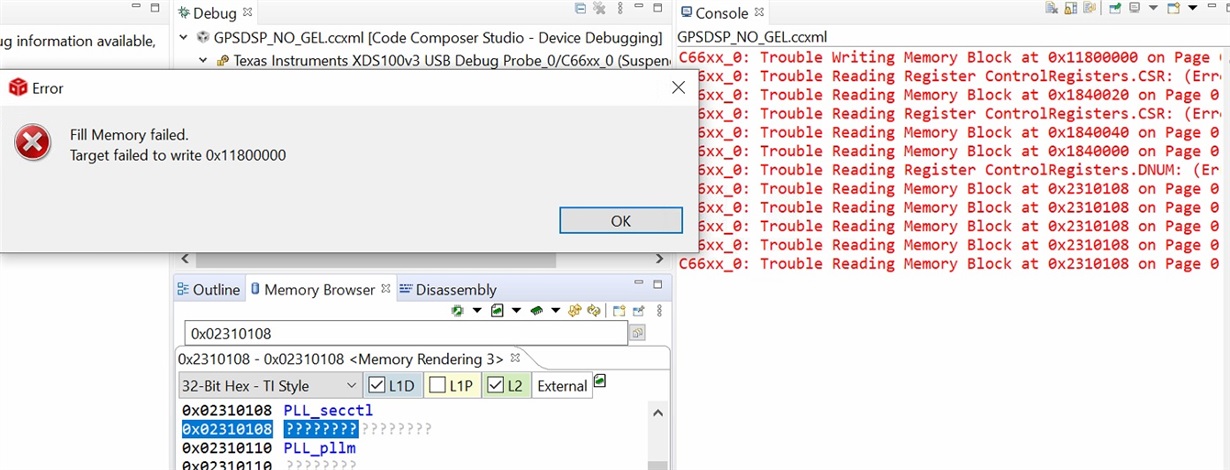

but when I try to connect to one of the cores - for core 1 i get the error:

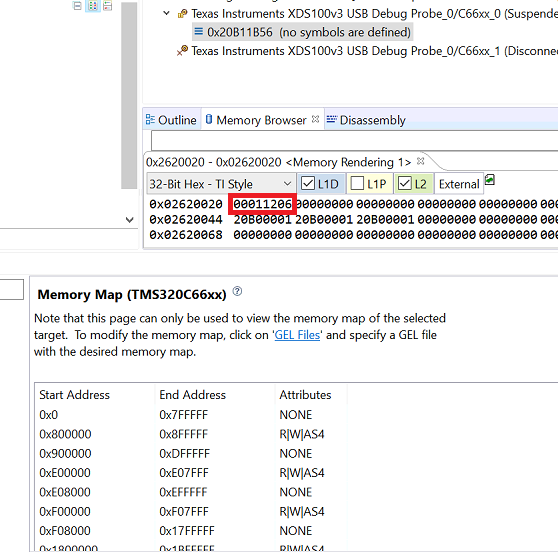

C66xx_1: Trouble Writing Memory Block at 0x800000 on Page 0 of Length 0x7ff0: (Error -1189 @ 0x800000) Requested operation failed for security violation. Check security/privilege settings, and retry the operation. (Emulation package 9.2.0.00002)

C66xx_1: File Loader: Verification failed: Target failed to write 0x00800000

C66xx_1: GEL: File: C:\ti\DSP_Tests Codes\test1.out: Load failed.

when i try to connect to core 0 - i get the error:

Error connecting to the target:

(Error -1143 @ 0x0)

Device core was hung. The debugger has forced the device to a ready state and recovered debug control, but your application's state is now corrupt. You should have limited access to memory and registers, but you may need to reset the device to debug further.

(Emulation package 9.2.0.00002)

C66xx_1: Power Failure on Target CPU

C66xx_1: Failed to remove the debug state from the target before disconnecting. There may still be breakpoint op-codes embedded in program memory. It is recommended that you reset the emulator before you connect and reload your program before you continue debugging

C66xx_0: Error connecting to the target: (Error -6306) Failed to connect to PRSC module. (Emulation package 9.2.0.00002)

Please advice what should i check.

Thanks,

Pavel