Other Parts Discussed in Thread: DRA829

Tool/software: TI C/C++ Compiler

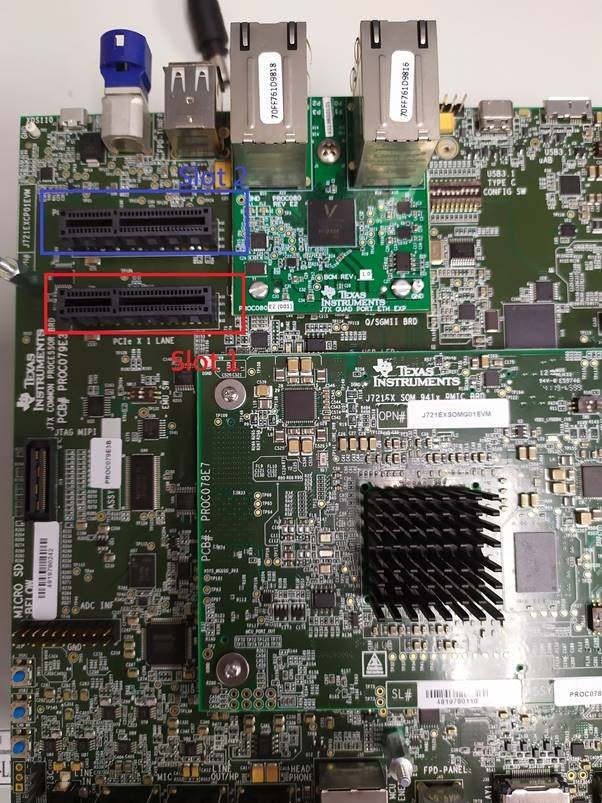

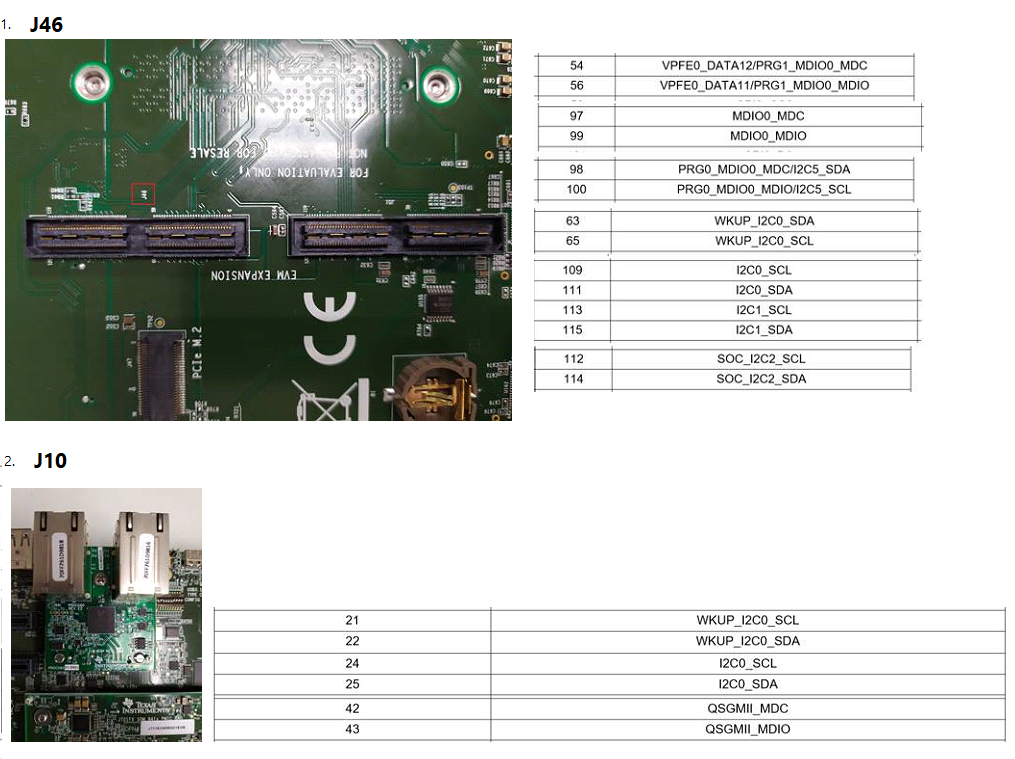

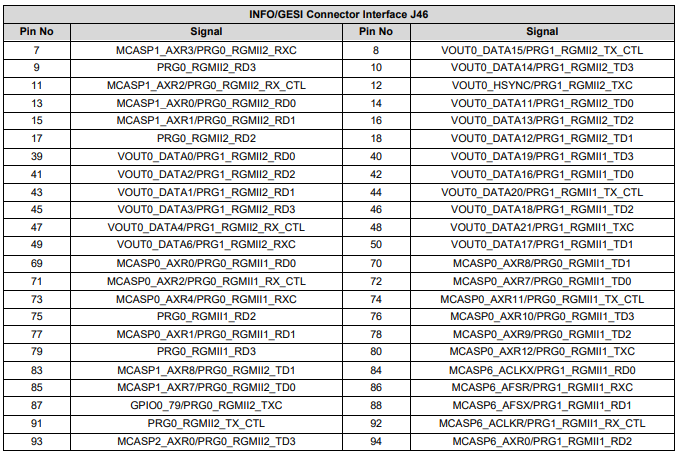

I want to get the pins related with MDIO of "PCIe x 2 LANE" to operate MDIO functions.

The MDIO pins seem to be GPIO pins connected with MCU, right?

It is because I saw only one MDIO bus in u-boot.

- u-boot

=> mdio list

ethernet@046000000:

0 - TI DP83867 <--> ethernet@046000000

However, I didn't see any GPIO information on EVM. Do you have any ideas?

- Linux

# ls -al /sys/class/gpio/

total 0

drwxr-xr-x 2 root root 0 Jun 17 14:17 .

drwxr-xr-x 61 root root 0 Jun 17 14:17 ..

--w------- 1 root root 65536 Jun 17 14:24 export

lrwxrwxrwx 1 root root 0 Jun 17 14:17 gpiochip284 -> ../../devices/platform/interconnect@100000/2010000.i2c/i2c-4/4-0020/gpio/gpiochip284

lrwxrwxrwx 1 root root 0 Jun 17 14:17 gpiochip292 -> ../../devices/platform/interconnect@100000/601000.gpio/gpio/gpiochip292

lrwxrwxrwx 1 root root 0 Jun 17 14:17 gpiochip328 -> ../../devices/platform/interconnect@100000/600000.gpio/gpio/gpiochip328

lrwxrwxrwx 1 root root 0 Jun 17 14:17 gpiochip456 -> ../../devices/platform/interconnect@100000/2060000.i2c/i2c-9/9-0020/gpio/gpiochip456

lrwxrwxrwx 1 root root 0 Jun 17 14:17 gpiochip464 -> ../../devices/platform/interconnect@100000/2030000.i2c/i2c-6/6-0020/gpio/gpiochip464

lrwxrwxrwx 1 root root 0 Jun 17 14:17 gpiochip472 -> ../../devices/platform/interconnect@100000/2000000.i2c/i2c-3/3-0022/gpio/gpiochip472

lrwxrwxrwx 1 root root 0 Jun 17 14:17 gpiochip496 -> ../../devices/platform/interconnect@100000/2000000.i2c/i2c-3/3-0020/gpio/gpiochip496

--w------- 1 root root 65536 Jun 17 14:17 unexport