We are using a 3.5" LCD with a 18bpp interface. The processor outputs 24bpp from the processor and connect only the 6 MSB of each color to the LCD connector.

We have a custom driver for the LCD with the display mode set up specifically for this display:

static const struct drm_display_mode default_mode = {

.clock = 10563, // Pixel Clock = 10.563MHz

.hdisplay = 320,

.hsync_start = 320 + 38, // Horizontal Back Porch = 38

.hsync_end = 320 + 38 + 2, // Horizontal Front Porch = 2

.htotal = 320 + 38 + 2 + 4, // Horizontal Sync = 4

.vdisplay = 480,

.vsync_start = 480 + 8, // Vertical Back Porch = 8

.vsync_end = 480 + 8 + 4, // Vertical Front Portch = 4

.vtotal = 480 + 8 + 4 + 4, // Vertical Sync = 4

.vrefresh = 60,

.flags = DRM_MODE_FLAG_NVSYNC | DRM_MODE_FLAG_NHSYNC,

};

Here is the output of my gfx_check.sh:

./gfx_check.sh WSEGL settings [default] WindowSystem=libpvrDRMWSEGL.so DefaultPixelFormat=ARGB8888 ------ ARM CPU information processor : 0 model name : ARMv7 Processor rev 2 (v7l) BogoMIPS : 597.60 Features : half thumb fastmult vfp edsp neon vfpv3 tls vfpd32 CPU implementer : 0x41 CPU architecture: 7 CPU variant : 0x3 CPU part : 0xc08 CPU revision : 2 Hardware : Generic AM33XX (Flattened Device Tree) Revision : 0000 Serial : 34:03:de:73:a9:65 ------ SGX driver information Version SGX_DDK_Linux_XOrg sgxddk 1.17@4948957 (release) omap_linux System Version String: SGX revision = 125 ------ Framebuffer settings mode "320x480-0" # D: 0.000 MHz, H: 0.000 kHz, V: 0.000 Hz geometry 320 480 320 480 32 timings 0 0 0 0 0 0 0 accel true rgba 8/16,8/8,8/0,0/0 endmode ------ Rotation settings 0 ------ Kernel Module information Module Size Used by g_mass_storage 16384 0 usb_f_mass_storage 45056 2 g_mass_storage libcomposite 53248 2 g_mass_storage,usb_f_mass_storage musb_dsps 20480 0 musb_hdrc 73728 1 musb_dsps pm33xx 16384 0 wkup_m3_ipc 16384 1 pm33xx wkup_m3_rproc 16384 1 pvrsrvkm 397312 0 remoteproc 45056 2 wkup_m3_rproc,wkup_m3_ipc omap_aes_driver 24576 0 ti_emif_sram 16384 1 pm33xx crypto_engine 16384 1 omap_aes_driver omap_sham 28672 0 omap_crypto 16384 1 omap_aes_driver goodix 20480 0 rtc_omap 20480 1 musb_am335x 16384 0 omap_wdt 16384 0 sch_fq_codel 20480 1 ------ Boot settings console=ttyO0,115200n8 root=PARTUUID=9066e1f1-02 rw rootfstype=ext4 rootwait ------ Linux Kernel version Linux ercss5 4.19.38-g4dae378bbe #1 PREEMPT Wed Sep 30 16:46:51 UTC 2020 armv7l GNU/Linux

The output of my qt_env.sh file:

#!/bin/sh ### QT Environment Variables ### export QT_QPA_EVDEV_TOUCHSCREEN_PARAMETERS="rotate=180" export SSL_CERT_FILE=/etc/ssl/certs/ca-certificates.crt export QT_QPA_EGLFS_KMS_CONFIG=/etc/qt5/eglfs_kms_cfg.json export QT_QPA_EGLFS_INTEGRATION=none export QT_QPA_PLATFORM=eglfs export QT_QPA_EGLFS_PHYSICAL_HEIGHT=49 export QT_QPA_EGLFS_PHYSICAL_WIDTH=73 export QT_QPA_EGLFS_DEBUG=1 export QSG_INFO=1

And the Qt debug output when running the application:

qt.scenegraph.general: threaded render loop qt.scenegraph.general: Using sg animation driver qt.scenegraph.general: Animation Driver: using vsync: 16.67 ms Created context for format QSurfaceFormat(version 2.0, options QFlags<QSurfaceFormat::FormatOption>(), depthBufferSize 24, redBufferSize -1, greenBufferSize -1, blueBufferSize -1, alphaBufferSize -1, stencilBufferSize 8, samples -1, swapBehavior QSurfaceFormat::SwapBehavior(DoubleBuffer), swapInterval 1, colorSpace QSurfaceFormat::ColorSpace(DefaultColorSpace), profile QSurfaceFormat::OpenGLContextProfile(NoProfile)) with config: EGL_BUFFER_SIZE: 32 EGL_ALPHA_SIZE: 8 EGL_BLUE_SIZE: 8 EGL_GREEN_SIZE: 8 EGL_RED_SIZE: 8 EGL_DEPTH_SIZE: 24 EGL_STENCIL_SIZE: 8 EGL_CONFIG_CAVEAT: 12344 EGL_CONFIG_ID: 8 EGL_LEVEL: 0 EGL_MAX_PBUFFER_HEIGHT: 2048 EGL_MAX_PBUFFER_PIXELS: 4194304 EGL_MAX_PBUFFER_WIDTH: 2048 EGL_NATIVE_RENDERABLE: 0 EGL_NATIVE_VISUAL_ID: 0 EGL_NATIVE_VISUAL_TYPE: 0 EGL_SAMPLES: 0 EGL_SAMPLE_BUFFERS: 0 EGL_SURFACE_TYPE: 1541 EGL_TRANSPARENT_TYPE: 12344 EGL_TRANSPARENT_BLUE_VALUE: 0 EGL_TRANSPARENT_GREEN_VALUE: 0 EGL_TRANSPARENT_RED_VALUE: 0 EGL_BIND_TO_TEXTURE_RGB: 0 EGL_BIND_TO_TEXTURE_RGBA: 0 EGL_MIN_SWAP_INTERVAL: 1 EGL_MAX_SWAP_INTERVAL: 10 qt.scenegraph.general: Using sg animation driver qt.scenegraph.general: Animation Driver: using vsync: 16.67 ms qt.scenegraph.general: texture atlas dimensions: 512x512 qt.scenegraph.general: R/G/B/A Buffers: 8 8 8 8 qt.scenegraph.general: Depth Buffer: 24 qt.scenegraph.general: Stencil Buffer: 8 qt.scenegraph.general: Samples: 0 qt.scenegraph.general: GL_VENDOR: Imagination Technologies qt.scenegraph.general: GL_RENDERER: PowerVR SGX 530 qt.scenegraph.general: GL_VERSION: OpenGL ES 2.0 build 1.17@4948957 qt.scenegraph.general: GL_EXTENSIONS: GL_OES_depth24 GL_OES_surfaceless_context GL_OES_texture_float GL_IMG_uniform_buffer_object GL_OES_element_index_uint GL_OES_rgb8_rgba8 GL_IMG_read_format GL_OES_fbo_render_mipmap GL_OES_depth_texture GL_KHR_debug GL_OES_texture_half_float GL_EXT_shader_texture_lod GL_OES_EGL_image_external GL_OES_standard_derivatives GL_IMG_texture_compression_pvrtc GL_IMG_texture_format_BGRA8888 GL_IMG_texture_npot GL_OES_packed_depth_stencil GL_EXT_texture_rg GL_IMG_multisampled_render_to_texture GL_IMG_program_binary GL_OES_vertex_half_float GL_EXT_texture_storage GL_OES_egl_sync GL_OES_fragment_precision_high GL_EXT_multisampled_render_to_texture GL_OES_mapbuffer GL_OES_EGL_image GL_OES_vertex_array_object GL_EXT_texture_format_BGRA8888 GL_EXT_multi_draw_arrays GL_IMG_shader_binary GL_OES_compressed_ETC1_RGB8_texture GL_EXT_blend_minmax GL_OES_get_program_binary GL_OES_required_internalformat GL_EXT_discard_framebuffer qt.scenegraph.general: Max Texture Size: 2048 qt.scenegraph.general: Debug context: false

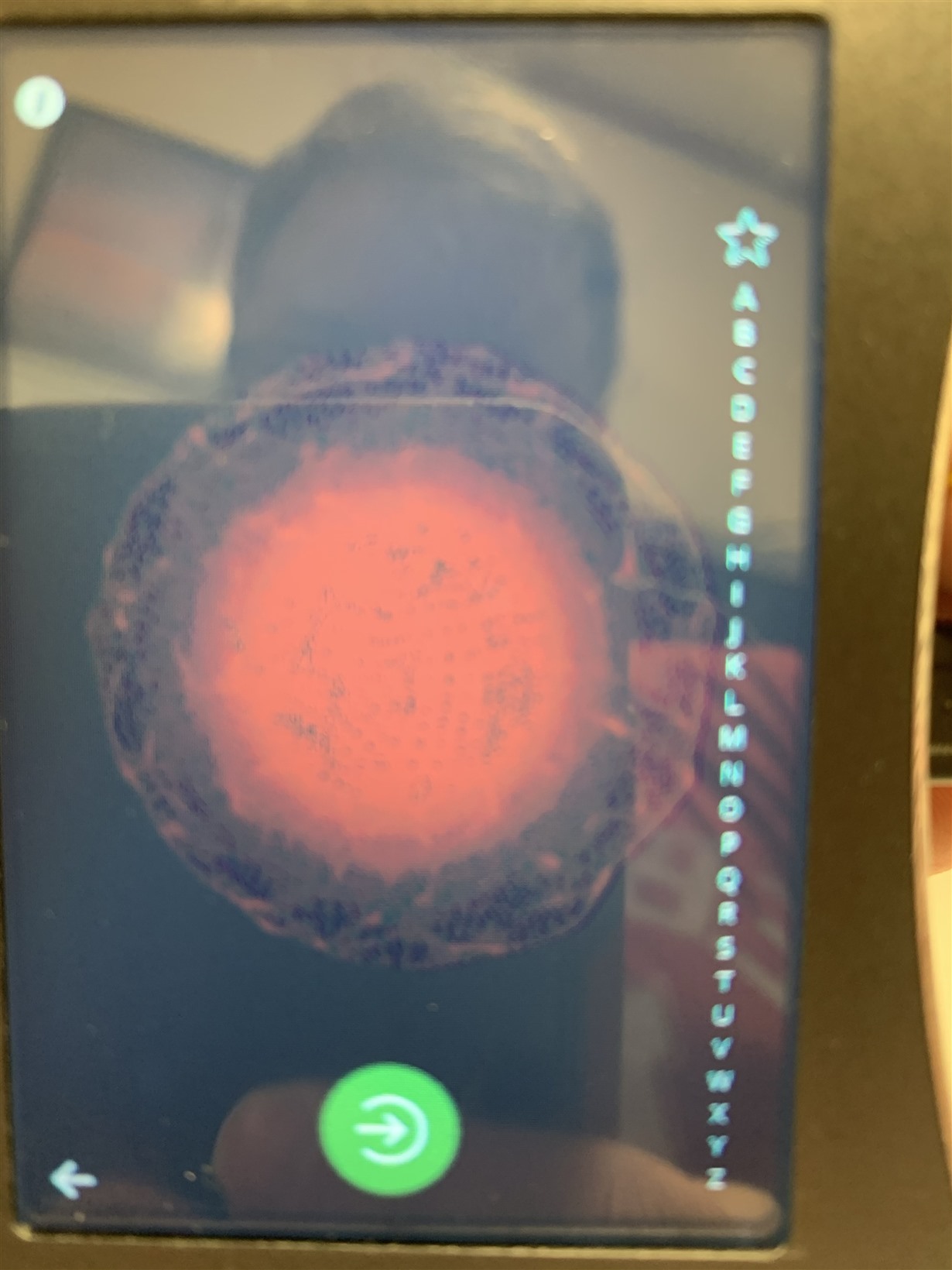

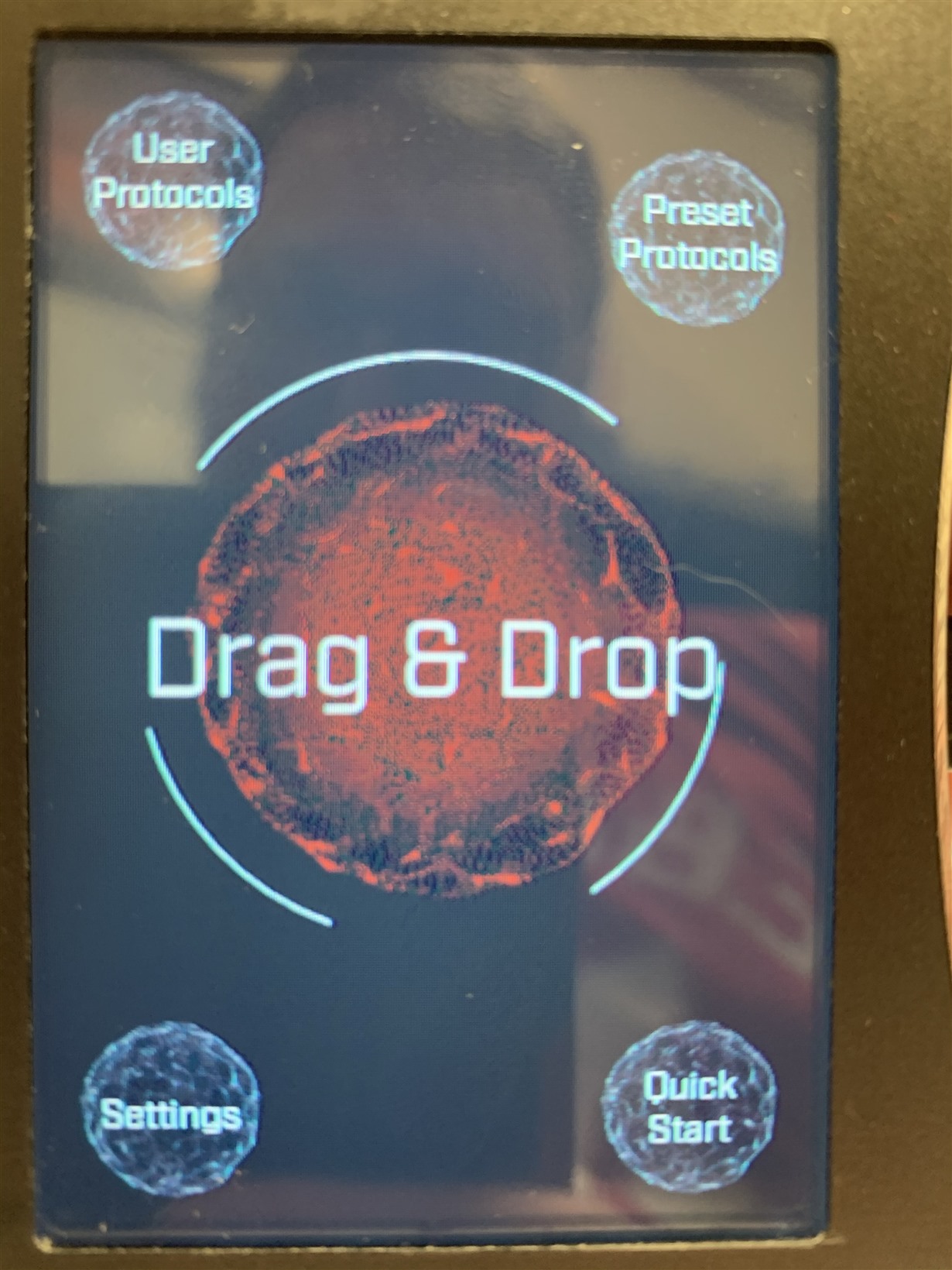

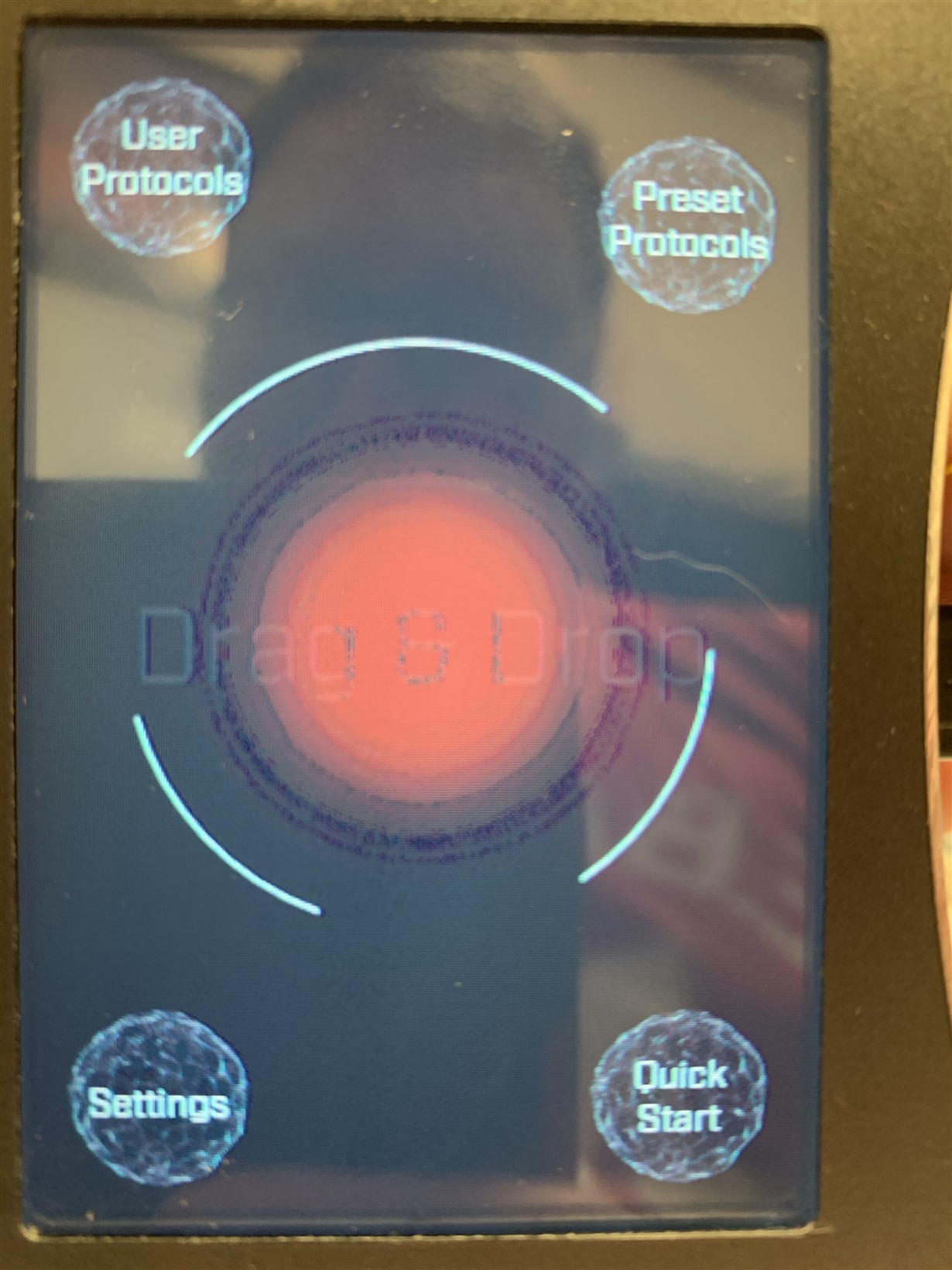

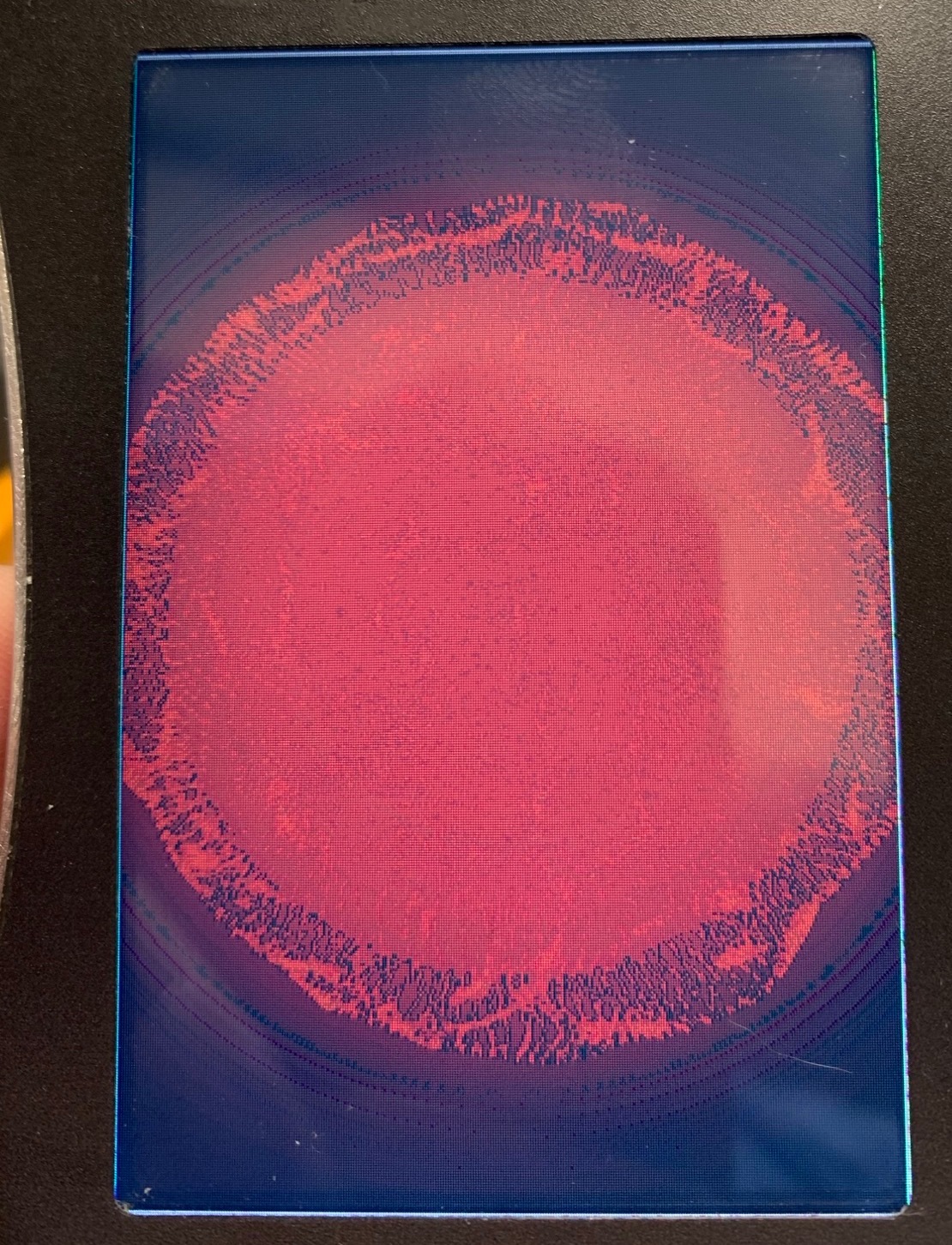

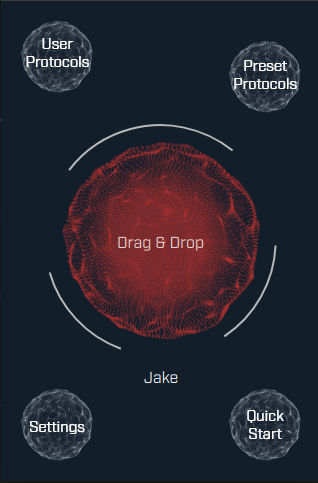

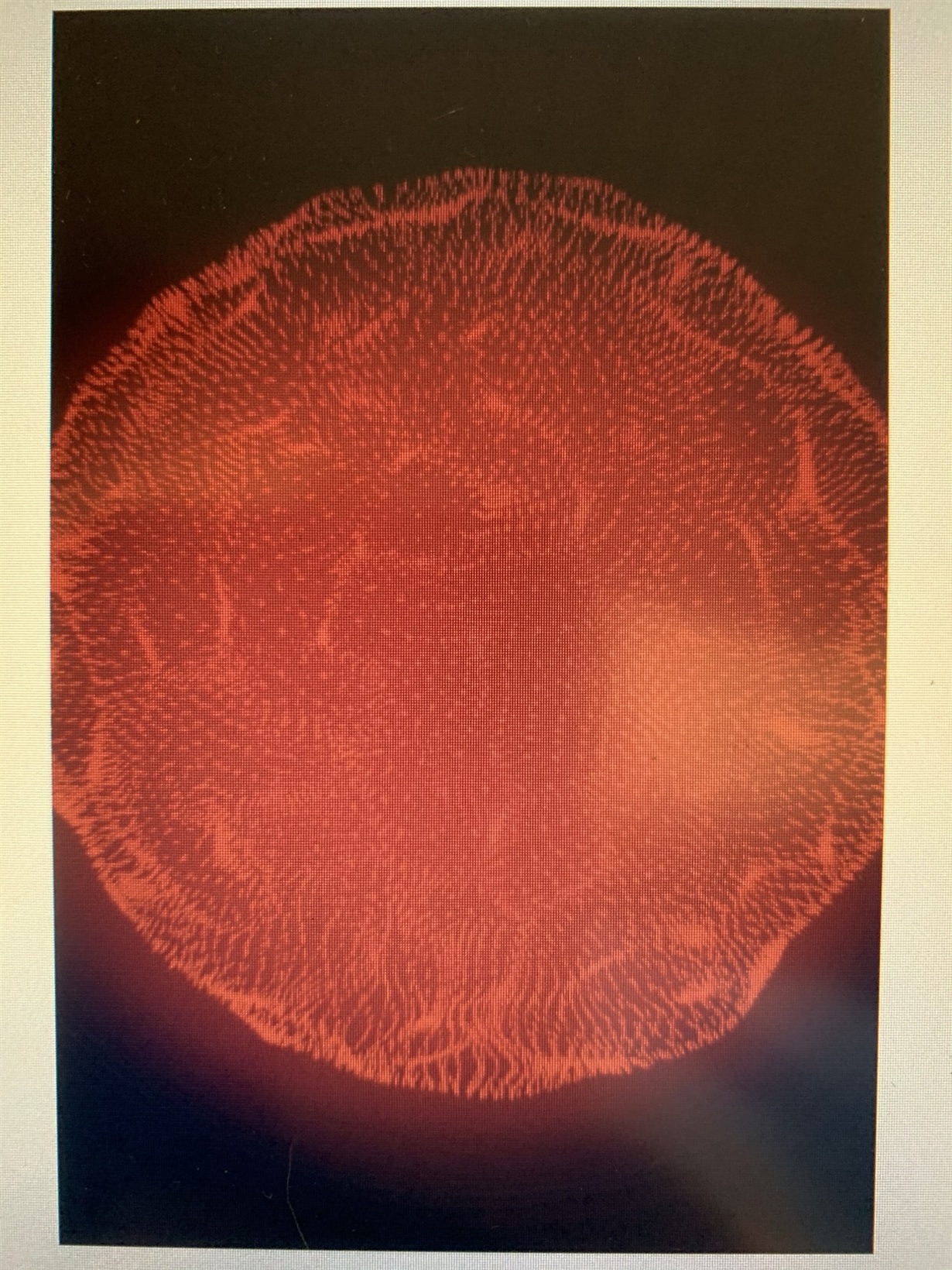

Finally, here are some images describing the color issues. The center circle is supposed to be a subtle fade from red to the background color and looks proper when run on a PC. The black artifacts in the "orb" aren't supposed to be there either.:

Thank you for any help,

Jake