Hello,

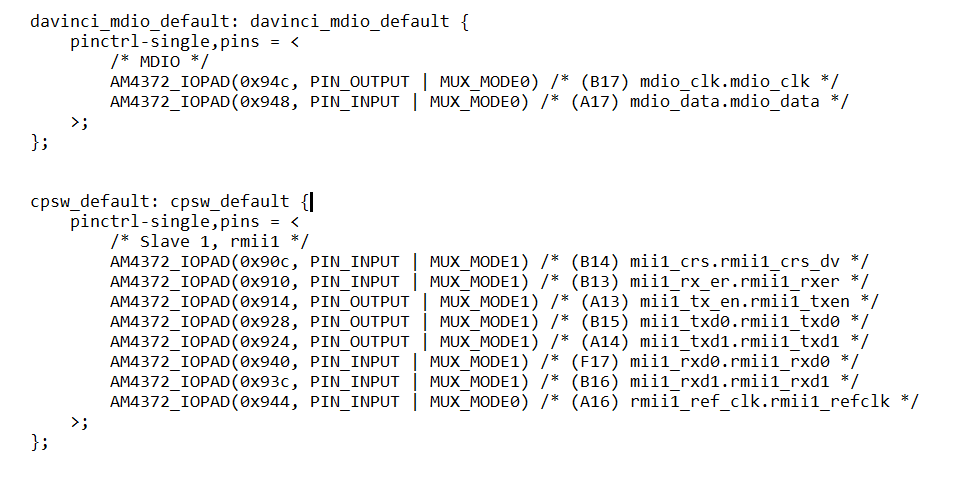

Customer used his own am4372 board, u-boot 2013.10, below is the PinMUX for rmii in mux.c:

static struct module_pin_mux henry_rmii1_pin_mux[] = {

{OFFSET(mii1_txd1), MODE(1)}, /* RMII1_TD1 */

{OFFSET(mii1_txd0), MODE(1)}, /* RMII1_TD0 */

{OFFSET(mii1_rxd1), MODE(1) | RXACTIVE}, /* RMII1_RD1 */

{OFFSET(mii1_rxd0), MODE(1) | RXACTIVE}, /* RMII1_RD0 */

{OFFSET(mii1_crs), MODE(1) | RXACTIVE}, /* RMII1_CRS_DV */

{OFFSET(mii1_txen), MODE(1)}, /* RMII1_TXEN */

{OFFSET(mii1_rxerr), MODE(1) | RXACTIVE}, /* RMII1_RXERR */

{OFFSET(rmii1_refclk), MODE(0) | RXACTIVE}, /* RMII1_refclk */

{-1},

};

MDIO pinmux:

static struct module_pin_mux mdio_pin_mux[] = {

{OFFSET(mdio_data), MODE(0) | RXACTIVE | PULLUP_EN},/* MDIO_DATA */

{OFFSET(mdio_clk), MODE(0) | PULLUP_EN}, /* MDIO_CLK */

{-1},

};

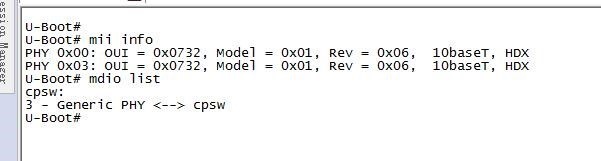

In u-boot, use mii command, it can find two PHY, but in fact there is only one ethernet with PHY address: 3.

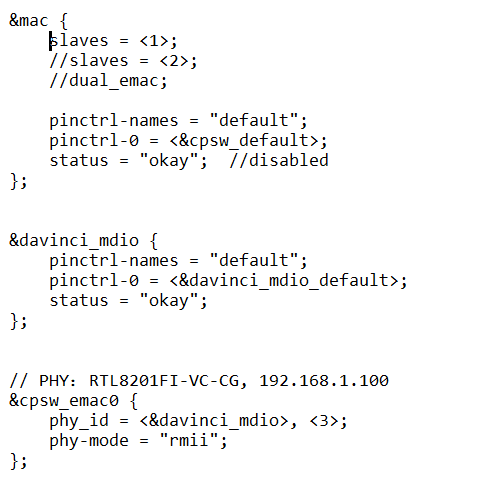

Linux version is 4.19.94,mii configuration in dts:

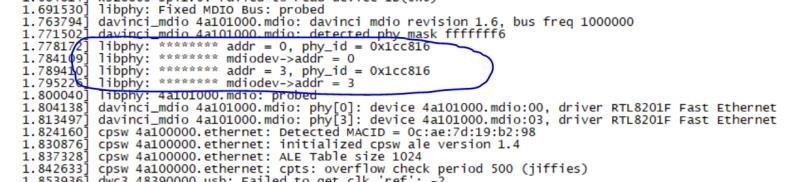

In kernel, MDIO find two PHY too.

What's reason it can find the address 0 PHY?

Thanks.

Rgds

Shine