Other Parts Discussed in Thread: TPD12S015,

Tool/software: Linux

Hi,

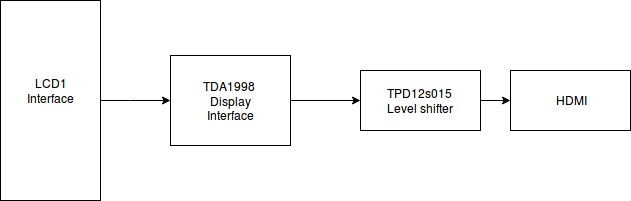

We intent to use the lcd1 interface for hdmi on our custom board.

The block diagram of the circuit is as follows,

We have made required changes in the pin mux and added lcd node in the device tree.

/*

* Copyright (C) 2017 Texas Instruments Incorporated - http://www.ti.com/

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License version 2 as

* published by the Free Software Foundation.

*/

/dts-v1/;

#include "dra76x.dtsi"

#include "dra7-evm-common.dtsi"

#include "dra76x-mmc-iodelay.dtsi"

#include <dt-bindings/net/ti-dp83867.h>

#include <dt-bindings/display/tda998x.h>

/ {

model = "TI DRA762 EVM";

compatible = "ti,dra76-evm", "ti,dra762", "ti,dra7";

aliases {

display0 = &hdmi0;

display1 = &lcd;

sound0 = &sound0;

sound1 = &hdmi;

rtc = &pcf85063;

};

memory@0 {

device_type = "memory";

reg = <0x0 0x80000000 0x0 0x80000000>;

};

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

ipu2_cma_pool: ipu2_cma@95800000 {

compatible = "shared-dma-pool";

reg = <0x0 0x95800000 0x0 0x3800000>;

reusable;

status = "okay";

};

dsp1_cma_pool: dsp1_cma@99000000 {

compatible = "shared-dma-pool";

reg = <0x0 0x99000000 0x0 0x4000000>;

reusable;

status = "okay";

};

ipu1_cma_pool: ipu1_cma@9d000000 {

compatible = "shared-dma-pool";

reg = <0x0 0x9d000000 0x0 0x2000000>;

reusable;

status = "okay";

};

dsp2_cma_pool: dsp2_cma@9f000000 {

compatible = "shared-dma-pool";

reg = <0x0 0x9f000000 0x0 0x800000>;

reusable;

status = "okay";

};

};

vsys_12v0: fixedregulator-vsys12v0 {

/* main supply */

compatible = "regulator-fixed";

regulator-name = "vsys_12v0";

regulator-min-microvolt = <12000000>;

regulator-max-microvolt = <12000000>;

regulator-always-on;

regulator-boot-on;

};

vsys_5v0: fixedregulator-vsys5v0 {

/* Output of Cntlr B of TPS43351-Q1 on dra76-evm */

compatible = "regulator-fixed";

regulator-name = "vsys_5v0";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

vin-supply = <&vsys_12v0>;

regulator-always-on;

regulator-boot-on;

};

vio_3v6: fixedregulator-vio_3v6 {

compatible = "regulator-fixed";

regulator-name = "vio_3v6";

regulator-min-microvolt = <3600000>;

regulator-max-microvolt = <3600000>;

vin-supply = <&vsys_5v0>;

regulator-always-on;

regulator-boot-on;

};

vsys_3v3: fixedregulator-vsys3v3 {

/* Output of Cntlr A of TPS43351-Q1 on dra76-evm */

compatible = "regulator-fixed";

regulator-name = "vsys_3v3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

vin-supply = <&vsys_12v0>;

regulator-always-on;

regulator-boot-on;

};

vio_3v3: fixedregulator-vio_3v3 {

compatible = "regulator-fixed";

regulator-name = "vio_3v3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

vin-supply = <&vsys_3v3>;

regulator-always-on;

regulator-boot-on;

};

vio_3v3_sd: fixedregulator-sd {

compatible = "regulator-fixed";

regulator-name = "vio_3v3_sd";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

vin-supply = <&vio_3v3>;

enable-active-high;

gpio = <&gpio4 21 GPIO_ACTIVE_HIGH>;

};

vio_1v8: fixedregulator-vio_1v8 {

compatible = "regulator-fixed";

regulator-name = "vio_1v8";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

vin-supply = <&smps5_reg>;

};

wlan_regulator: fixedregulator-wlan_regulator {

compatible = "regulator-fixed";

regulator-name = "wlan_regulator";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

regulator-always-on;

regulator-boot-on;

/*gpio = <&gpio3 29 GPIO_ACTIVE_HIGH>;

enable-active-high;*/

};

vmmcwl_fixed: fixedregulator-mmcwl {

compatible = "regulator-fixed";

regulator-name = "vmmcwl_fixed";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

gpio = <&gpio5 8 0>; /* gpio5_8 */

startup-delay-us = <70000>;

enable-active-high;

};

vtt_fixed: fixedregulator-vtt {

compatible = "regulator-fixed";

regulator-name = "vtt_fixed";

regulator-min-microvolt = <1350000>;

regulator-max-microvolt = <1350000>;

vin-supply = <&vsys_3v3>;

regulator-always-on;

regulator-boot-on;

};

aic_dvdd: fixedregulator-aic_dvdd {

/* TPS77018DBVT */

compatible = "regulator-fixed";

regulator-name = "aic_dvdd";

vin-supply = <&vio_3v3>;

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

};

lcd: display {

/*

* TODO: Not a DPI panel, but a dummy DSI video mode panel.

* This needs to be changed later when we can support DSI VM

* panels properly.

*/

compatible = "osd,osd101t2045-53ts", "panel-dpi";

label = "lcd";

/*backlight = <&lcd_bl>;*/

panel-timing {

clock-frequency = <154000000>;

hactive = <1920>;

vactive = <1200>;

hfront-porch = <112>;

hback-porch = <32>;

hsync-len = <16>;

vfront-porch = <16>;

vback-porch = <16>;

vsync-len = <2>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <1>;

pixelclk-active = <1>;

};

port {

lcd_in: endpoint {

remote-endpoint = <&hdmi_0>;

};

};

};

hdmi0: connector {

compatible = "hdmi-connector";

label = "hdmi";

type = "a";

port {

hdmi_connector_in: endpoint {

remote-endpoint = <&tpd12s015_out>;

};

};

};

tpd12s015: encoder {

compatible = "ti,tpd12s015";

gpios = <&gpio7 30 GPIO_ACTIVE_HIGH>, /* gpio7_30, CT CP HPD */

<&gpio7 31 GPIO_ACTIVE_HIGH>, /* gpio7_31, LS OE */

<&gpio7 12 GPIO_ACTIVE_HIGH>; /* gpio7_12/sp1_cs2, HPD */

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

tpd12s015_in: endpoint {

remote-endpoint = <&hdmi_out>;

};

};

port@1 {

reg = <1>;

tpd12s015_out: endpoint {

remote-endpoint = <&hdmi_connector_in>;

};

};

};

};

};

&i2c1 {

status = "okay";

clock-frequency = <400000>;

tps65917: tps65917@58 {

compatible = "ti,tps65917";

reg = <0x58>;

ti,system-power-controller;

ti,palmas-override-powerhold;

interrupt-controller;

#interrupt-cells = <2>;

tps65917_pmic {

compatible = "ti,tps65917-pmic";

smps12-in-supply = <&vsys_3v3>;

smps3-in-supply = <&vsys_3v3>;

smps4-in-supply = <&vsys_3v3>;

smps5-in-supply = <&vsys_3v3>;

ldo1-in-supply = <&vsys_3v3>;

ldo2-in-supply = <&vsys_3v3>;

ldo3-in-supply = <&vsys_5v0>;

ldo4-in-supply = <&vsys_5v0>;

ldo5-in-supply = <&vsys_3v3>;

tps65917_regulators: regulators {

smps12_reg: smps12 {

/* VDD_DSPEVE */

regulator-name = "smps12";

regulator-min-microvolt = <850000>;

regulator-max-microvolt = <1250000>;

regulator-always-on;

regulator-boot-on;

};

smps3_reg: smps3 {

/* VDD_CORE */

regulator-name = "smps3";

regulator-min-microvolt = <850000>;

regulator-max-microvolt = <1250000>;

regulator-boot-on;

regulator-always-on;

};

smps4_reg: smps4 {

/* VDD_IVA */

regulator-name = "smps4";

regulator-min-microvolt = <850000>;

regulator-max-microvolt = <1250000>;

regulator-always-on;

regulator-boot-on;

};

smps5_reg: smps5 {

/* VDDS1V8 */

regulator-name = "smps5";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

regulator-boot-on;

regulator-always-on;

};

ldo1_reg: ldo1 {

/* LDO1_OUT --> VDA_PHY1_1V8 */

regulator-name = "ldo1";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

regulator-always-on;

regulator-boot-on;

regulator-allow-bypass;

};

ldo2_reg: ldo2 {

/* LDO2_OUT --> VDA_PHY2_1V8 */

regulator-name = "ldo2";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

regulator-allow-bypass;

regulator-always-on;

};

ldo3_reg: ldo3 {

/* VDA_USB_3V3 */

regulator-name = "ldo3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

regulator-boot-on;

regulator-always-on;

};

ldo5_reg: ldo5 {

/* VDDA_1V8_PLL */

regulator-name = "ldo5";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <1800000>;

regulator-always-on;

regulator-boot-on;

};

ldo4_reg: ldo4 {

/* VDD_SDIO_DV */

regulator-name = "ldo4";

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <3300000>;

regulator-boot-on;

regulator-always-on;

};

};

};

tps65917_power_button {

compatible = "ti,palmas-pwrbutton";

interrupt-parent = <&tps65917>;

interrupts = <1 IRQ_TYPE_NONE>;

wakeup-source;

ti,palmas-long-press-seconds = <6>;

};

};

lp87565: lp87565@60 {

compatible = "ti,lp87565-q1";

reg = <0x60>;

buck10-in-supply =<&vsys_3v3>;

buck23-in-supply =<&vsys_3v3>;

regulators: regulators {

buck10_reg: buck10 {

/*VDD_MPU*/

regulator-name = "buck10";

regulator-min-microvolt = <850000>;

regulator-max-microvolt = <1250000>;

regulator-always-on;

regulator-boot-on;

};

buck23_reg: buck23 {

/* VDD_GPU*/

regulator-name = "buck23";

regulator-min-microvolt = <850000>;

regulator-max-microvolt = <1250000>;

regulator-boot-on;

regulator-always-on;

};

};

};

pcf_lcd: pcf8757@20 {

compatible = "ti,pcf8575", "nxp,pcf8575";

reg = <0x20>;

gpio-controller;

#gpio-cells = <2>;

interrupt-controller;

#interrupt-cells = <2>;

interrupt-parent = <&gpio1>;

interrupts = <3 IRQ_TYPE_EDGE_FALLING>;

status = "disabled";

};

pcf_gpio_21: pcf8757@21 {

compatible = "ti,pcf8575", "nxp,pcf8575";

reg = <0x21>;

gpio-controller;

#gpio-cells = <2>;

interrupt-parent = <&gpio1>;

interrupts = <3 IRQ_TYPE_EDGE_FALLING>;

interrupt-controller;

#interrupt-cells = <2>;

status = "disabled";

};

pcf_hdmi: pcf8575@26 {

compatible = "ti,pcf8575", "nxp,pcf8575";

reg = <0x26>;

gpio-controller;

#gpio-cells = <2>;

status = "disabled";

p1 {

/* vin6_sel_s0: high: VIN6, low: audio */

gpio-hog;

gpios = <1 GPIO_ACTIVE_HIGH>;

output-low;

line-name = "vin6_sel_s0";

};

};

tlv320aic3106: tlv320aic3106@19 {

#sound-dai-cells = <0>;

compatible = "ti,tlv320aic3106";

reg = <0x19>;

adc-settle-ms = <40>;

ai3x-micbias-vg = <1>; /* 2.0V */

status = "okay";

/* Regulators */

AVDD-supply = <&vio_3v3>;

IOVDD-supply = <&vio_3v3>;

DRVDD-supply = <&vio_3v3>;

DVDD-supply = <&aic_dvdd>;

};

/****************************EEPROM*********************************/

eeprom: eeprom@50 {

compatible = "atmel,24c256";

reg = <0x50>;

};

/**********************Temp Sensor TMP102A*************************/

tmp102: tmp102@48 {

compatible = "ti,tmp102";

reg = <0x48>;

/* interrupt-parent = <&gpio2>;

interrupts = <16 IRQ_TYPE_LEVEL_LOW>;*/

#thermal-sensor-cells = <1>;

};

/******************************************************************/

};

/******************************TDA1988 Display Interface******************************************/

&i2c3 {

disp_ser: serializer@0c {

compatible = "ti,ds90ub921q";

reg = <0x0c>;

#address-cells = <1>;

#size-cells = <0>;

status = "disabled";

};

tda19988: tda19988 {

compatible = "nxp,tda998x";

reg = <0x70>;

/*pinctrl-names = "default", "off";

pinctrl-0 = <&nxp_hdmi_bonelt_pins>;

pinctrl-1 = <&nxp_hdmi_bonelt_off_pins>;*/

/* Convert 24bit BGR to RGB, e.g. cross red and blue wiring */

video-ports = <0x230145>;

#sound-dai-cells = <0>;

/*audio-ports = < TDA998x_I2S 0x03>; */

ports {

port@0 {

hdmi_0: endpoint@0 {

remote-endpoint = <&lcd_in>;

lanes = <0 1 2 3 4 5 6 7 8 9>;

};

};

};

};

};

/******************************RTC PCA85063 & ADC ADS1015******************************************/

&i2c4 {

status = "okay";

clock-frequency = <400000>;

pcf85063: rtc@51 {

status = "okay";

compatible = "nxp,pcf85063";

reg = <0x51>;

#clock-cells = <0>;

/*quartz-load-femtofarads = <12500>;*/

};

ads1015@49 {

compatible = "ti,ads1015";

reg = <0x48>;

#address-cells = <1>;

#size-cells = <0>;

channel@0 {

reg = <0>;

ti,gain = <3>;

ti,datarate = <5>;

};

channel@1 {

reg = <1>;

ti,gain = <3>;

ti,datarate = <5>;

};

channel@2 {

reg = <2>;

ti,gain = <3>;

ti,datarate = <5>;

};

channel@3 {

reg = <3>;

ti,gain = <3>;

ti,datarate = <5>;

};

channel@4 {

reg = <4>;

ti,gain = <2>;

ti,datarate = <5>;

};

channel@5 {

reg = <5>;

ti,gain = <2>;

ti,datarate = <5>;

};

channel@6 {

reg = <6>;

ti,gain = <3>;

ti,datarate = <5>;

};

channel@7 {

reg = <7>;

ti,gain = <3>;

ti,datarate = <5>;

};

};

};

/*************************************************************************************************/

&i2c5 {

status = "okay";

clock-frequency = <400000>;

ov10633@37 {

compatible = "ovti,ov10633";

reg = <0x37>;

clocks = <&clk_ov10633_fixed>;

clock-names = "xvclk";

mux-gpios = <&pcf_hdmi 2 GPIO_ACTIVE_HIGH>, /* VIN2_S0 */

<&pcf_hdmi 6 GPIO_ACTIVE_LOW>; /* VIN2_S2 */

port {

onboardLI: endpoint {

remote-endpoint = <&vin2a>;

hsync-active = <1>;

vsync-active = <1>;

pclk-sample = <0>;

};

};

};

gpio_csi2_adap: tca6416@20 {

status = "okay";

compatible = "ti,tca6416";

reg = <0x20>;

gpio-controller;

#gpio-cells = <2>;

};

ov490@24 {

compatible = "ovti,ov490";

reg = <0x24>;

mux-gpios = <&gpio_csi2_adap 0 GPIO_ACTIVE_LOW>,

/* CSI2_SEL_I2C_CLK */

<&gpio_csi2_adap 1 GPIO_ACTIVE_HIGH>,

/* CSI2_SEL_REF_CLK */

<&gpio_csi2_adap 3 GPIO_ACTIVE_HIGH>,

/* CSI2_CAM0_RESETn */

<&gpio_csi2_adap 4 GPIO_ACTIVE_LOW>;

/* CSI2_CAM0_PWR_DWN */

port {

csi2_cam0: endpoint@0 {

clock-lanes = <0>;

data-lanes = <1 2 3 4>;

remote-endpoint = <&csi2_phy0>;

};

};

};

};

&cpu0 {

vdd-supply = <&buck10_reg>;

};

&mmc1 {

status = "okay";

vmmc-supply = <&vio_3v3_sd>;

vmmc_aux-supply = <&ldo4_reg>;

bus-width = <4>;

/*

* SDCD signal is not being used here - using the fact that GPIO mode

* is always hardwired.

*/

cd-gpios = <&gpio6 27 GPIO_ACTIVE_LOW>;

max-frequency = <192000000>;

pinctrl-names = "default", "hs";

pinctrl-0 = <&mmc1_pins_default>;

pinctrl-1 = <&mmc1_pins_hs>;

};

&mmc2 {

status = "okay";

vmmc-supply = <&vio_1v8>;

bus-width = <8>;

max-frequency = <192000000>;

pinctrl-names = "default", "hs", "ddr_1_8v", "hs200_1_8v";

pinctrl-0 = <&mmc2_pins_default>;

};

/***********************Added for mmc3*******************************************************************/

&dra7_pmx_core {

mmc3_pins_default: mmc3_pins_default {

pinctrl-single,pins = <

DRA7XX_CORE_IOPAD(0x377c, (PIN_INPUT_PULLUP | MODE_SELECT | MUX_MODE0))

DRA7XX_CORE_IOPAD(0x3780, (PIN_INPUT_PULLUP | MODE_SELECT | MUX_MODE0))

DRA7XX_CORE_IOPAD(0x3784, (PIN_INPUT_PULLUP | MODE_SELECT | MUX_MODE0))

DRA7XX_CORE_IOPAD(0x3788, (PIN_INPUT_PULLUP | MODE_SELECT | MUX_MODE0))

DRA7XX_CORE_IOPAD(0x378c, (PIN_INPUT_PULLUP | MODE_SELECT | MUX_MODE0))

DRA7XX_CORE_IOPAD(0x3790, (PIN_INPUT_PULLUP | MODE_SELECT | MUX_MODE0))

>;

};

};

&mmc3{

status = "okay";

vmmc-supply = <&vio_3v3>;

/*vqmmc-supply = <&vio_1v8>;*/

vmmc_aux-supply = <&wlan_regulator>;

bus-width = <4>;

ti,non-removable;

max-frequency = <50000000>;

/*cap-sdio-irq;*/

cap-power-off-card;

keep-power-in-suspend;

/*enable-sdio-wakeup;*/

/*pinctrl-names = "default";

pinctrl-0 = <&mmc3_pins_default &mmc3_iodelay_manual1_conf>;

pinctrl-names = "default", "hs", "sdr12", "sdr25", "sdr50";

pinctrl-0 = <&mmc3_pins_default &mmc3_iodelay_manual1_conf>;

pinctrl-1 = <&mmc3_pins_hs &mmc3_iodelay_manual1_conf>;

pinctrl-2 = <&mmc3_pins_sdr12 &mmc3_iodelay_manual1_conf>;

pinctrl-3 = <&mmc3_pins_sdr25 &mmc3_iodelay_manual1_conf>;

pinctrl-4 = <&mmc3_pins_sdr50 &mmc3_iodelay_manual1_conf>;*/

};

/**************************************************************************************************************************/

&mmc4 {

status = "okay";

vmmc-supply = <&vio_3v6>;

vqmmc-supply = <&vmmcwl_fixed>;

pinctrl-names = "default", "hs", "sdr12", "sdr25";

pinctrl-0 = <&mmc4_pins_hs &mmc4_iodelay_default_conf>;

pinctrl-1 = <&mmc4_pins_hs &mmc4_iodelay_manual1_conf>;

pinctrl-2 = <&mmc4_pins_hs &mmc4_iodelay_manual1_conf>;

pinctrl-3 = <&mmc4_pins_hs &mmc4_iodelay_manual1_conf>;

};

/* No RTC on this device */

&rtc {

status = "disabled";

};

&mac {

status = "okay";

/*slaves = <1>;*/

dual_emac;

};

/*&cpsw_emac0 {

phy_id = <&davinci_mdio>, <2>;

phy-mode = "rgmii-id";

status="disabled";

dual_emac_res_vlan = <1>;

};*/

&cpsw_emac1 {

phy_id = <&davinci_mdio>, <3>;

phy-mode = "rgmii-id";

status="okay";

dual_emac_res_vlan = <2>;

};

&davinci_mdio {

dp83867_0: ethernet-phy@2 {

reg = <2>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_25_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_250_PS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_8_B_NIB>;

ti,min-output-impedance;

ti,dp83867-rxctrl-strap-quirk;

status = "disabled";

};

dp83867_1: ethernet-phy@3 {

reg = <3>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_25_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_250_PS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_8_B_NIB>;

ti,min-output-impedance;

ti,dp83867-rxctrl-strap-quirk;

status = "okay";

};

};

&usb2_phy1 {

phy-supply = <&ldo3_reg>;

};

&usb2_phy2 {

phy-supply = <&ldo3_reg>;

};

&dss {

status = "ok";

vdda_video-supply = <&ldo5_reg>;

};

&hdmi {

status = "ok";

vdda-supply = <&ldo1_reg>;

port {

hdmi_out: endpoint {

remote-endpoint = <&tpd12s015_in>;

};

};

};

&qspi {

spi-max-frequency = <96000000>;

m25p80@0 {

spi-max-frequency = <96000000>;

};

};

&m_can0 {

status = "okay";

can-transceiver {

max-bitrate = <5000000>;

};

};

&cal {

status = "okay";

};

&csi2_0 {

csi2_phy0: endpoint@0 {

slave-mode;

remote-endpoint = <&csi2_cam0>;

};

};

&vin2a {

status = "okay";

endpoint@0 {

slave-mode;

remote-endpoint = <&onboardLI>;

};

};

&ipu2 {

status = "okay";

memory-region = <&ipu2_cma_pool>;

};

&ipu1 {

status = "okay";

memory-region = <&ipu1_cma_pool>;

};

&dsp1 {

status = "okay";

memory-region = <&dsp1_cma_pool>;

};

&dsp2 {

status = "okay";

memory-region = <&dsp2_cma_pool>;

};

&pcie2_phy {

status = "okay";

};

&pcie1_rc {

num-lanes = <2>;

phys = <&pcie1_phy>, <&pcie2_phy>;

phy-names = "pcie-phy0", "pcie-phy1";

};

&pcie1_ep {

num-lanes = <2>;

phys = <&pcie1_phy>, <&pcie2_phy>;

phy-names = "pcie-phy0", "pcie-phy1";

};

/************************USB 3 & 4 ULPI Interface*****************************************/

&omap_dwc3_3 {

status = "okay";

snps,dis_u3_susphy_quirk;

snps,dis_u2_susphy_quirk;

};

&usb3 {

dr_mode = "host";

snps,hsphy_interface = "ulpi";

status = "okay";

cs-gpios = <&gpio5 16 GPIO_ACTIVE_HIGH>;

tx-fifo-resize;

phy {

compatible = "ti,tusb1210";

};

};

&omap_dwc3_4 {

status = "okay";

snps,dis_u3_susphy_quirk;

snps,dis_u2_susphy_quirk;

};

&usb4 {

dr_mode = "host";

snps,hsphy_interface = "ulpi";

status = "okay";

cs-gpios = <&gpio5 17 GPIO_ACTIVE_HIGH>;

snps,dis_u3_susphy_quirk;

snps,dis_u2_susphy_quirk;

tx-fifo-resize;

phy {

compatible = "ti,tusb1210";

};

};

/****************************************************************************************/

&extcon_usb1 {

compatible = "linux,extcon-usb-gpio";

vbus-gpio = <&gpio6 12 GPIO_ACTIVE_HIGH>;

id-gpio = <&gpio2 25 GPIO_ACTIVE_HIGH>;

};

/*&extcon_usb2 {

vbus-gpio = <&pcf_lcd 15 GPIO_ACTIVE_HIGH>;

};*/

We needed some guidance in device tree for bringing up the hdmi interface from lcd1 port.

Regards,

Padmesh