Hi Expert,

This is to confirm DRA750 I2C3 behavior (and it is related to DRA750: I2C3 behavior & How to recover from I2C issue)

Customer is using FAST mode on I2C3.

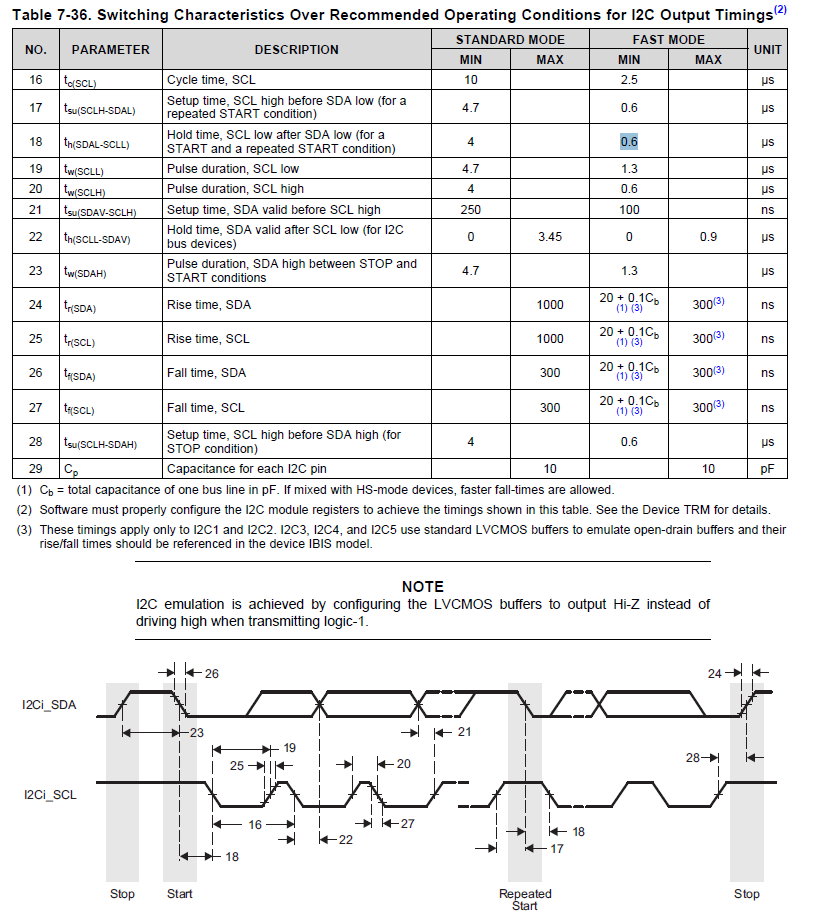

According to DRA75x DataManual Table 7-36 above, th(SDAL-SCLL) - Hold time SCL low after SDA low (for a START and a repeated START condition) needs 0.6usec or longer to enter into START condition.

[Question] In other words, if Jacinto-6 receives SDA/SCL with th(SDAL-SCLL) wihich is always less than 0.6usec, Jactinto6 I2C3 module will never recognize as START condition. Is that correct ?

External I2C slave device (called as CP), which is connected to Jacinto6 I2C3, makes both SCL and SDA pins to LOW level illegally after booting up.

Customer mentions that CP SCL and SDA output timing keeps th(SDAL-SCLL) less than 0.6usec. Thus, customer wants to confirm if Jacitno6 I2C3 has never enter into START condition or not.

Best regards,

Saito