Other Parts Discussed in Thread: XIO2001

Hello,

There is still an issue regarding the startup of our system, when there is a pcie-device TI xio2001 (pcie/pci bridge) connected.

Also see ticket https://e2e.ti.com/support/processors/f/791/t/942634

A brief architecture of our system:

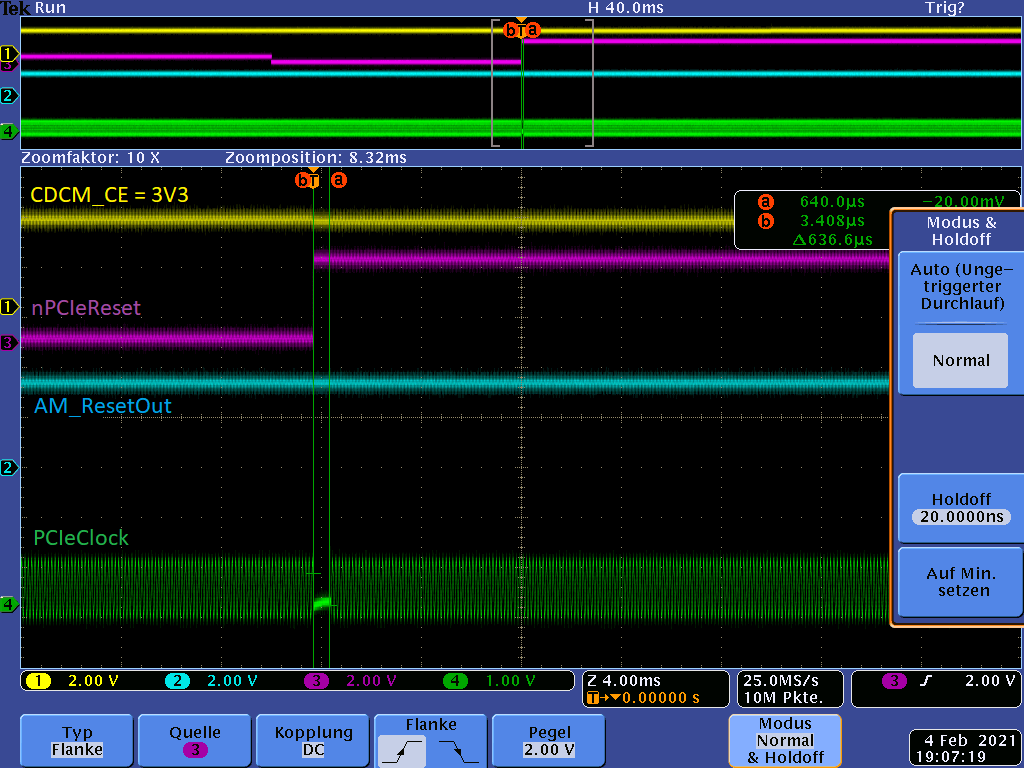

In the scope-picture we can see:

nGRST – indicates the internal Reset of the xio2001. It is only connected to capacitors.

nPCIeReset – this signal is controlled by the sitara. In this case we added a pulldown, so the signal is only released by the CPU

3V3 – this is our supply voltage, as you see it is stable

nPOR (PORz) – it is controlled by a voltage supply chip from power on and from a FPGA. We implement a watchdog in the FPGA, when the system is not starting

AM_CDCM_CE – is connected to the sitara and always stable

PCIeClock – unfortunately we can`t scope it well due to the sampling frequency.

When we want to read the pcie register the cpu stucks.

This problem is repeatable on some board very often (> 9 of 10 times) and on other boards (same hardware and software) the problem doesn’t occur.

We are booting from a spi flash

Thanks and regards

Chris