Other Parts Discussed in Thread: LMX2594

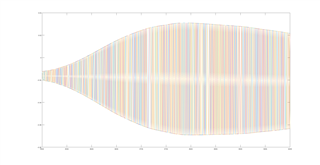

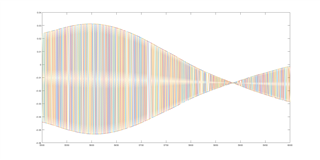

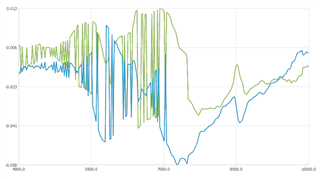

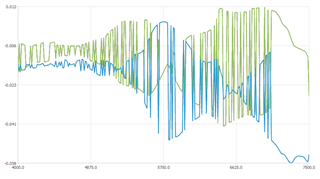

When setting the LO below 7500MHz, I'm seeing significant jumps in the IQ output between frequencies (custom board). These jumps are random and will change frequencies on subsequent sweeps (as you can kind of see here). If the jumps occurred throughout the entire bandwidth I'd start to suspect my ADC or backend processing, but the fact that it always settles out prior to the 7500MHz mark makes me start to suspect an issue with the DIV2 Quadrature generator. I've used the TICS Pro tool to setup my registers and I'm copying it's suggested register write order on the frequency change, but with no luck. I'm waiting until the VCO locks before I start my readings, so it shouldn't be an issue with an unstable output. Increasing my dwell time on each frequency (3ms-12ms) doesn't change the output at all.

Any suggestions on what I'm doing wrong? I suspect that it's a simple register issue somewhere, but the documentation for this device is spotty at best.