Hello,

we are facing some issues with the configuration of the AFE7444 installed in our board, but it is not fully clear the rootcause.

For debug purposes, we set the possibility to configure the device using the EVK FTDI (From J13, pins 1, 4, 7 and 10) controlled by the TI GUI (Mode6). With this setup the device is working properly (both on TX and RX chains).

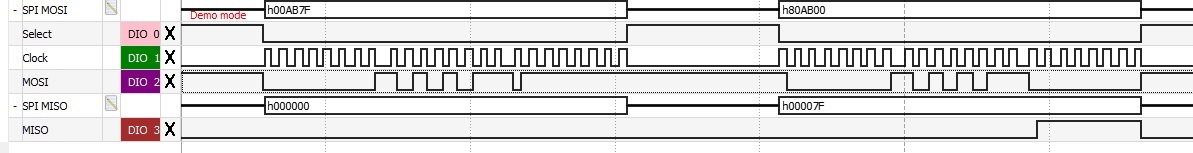

The issue happens when the SPI is controlled by the onboard processor: the driver that we are using doesn't support 24bits access, so we implemented 8+8+8 bit access, as shown in the picture (50us time scale, clock at 200kHz).

In order to debug, we read back the register value after each write access and we don't get any mismatch, unless for registers that are partially ReadOnly.

To set the register we parse the configuration file generated from the GUI (logFile_converted_to_low_level_read.cfg, attached)./cfs-file/__key/communityserver-discussions-components-files/220/logFile_5F00_converted_5F00_to_5F00_low_5F00_level_5F00_read.cfg

Please, do you think that the current implementation (3 times 8 clock cycle) might affect the reliability of the configuration?

Another point, from the EVK we measured, between each register access, a delay of minimum 30ms, is this delay strictly required to get a correct configuration?

Thank you in advance for the support

Kind regards

Massimo