Hi All,

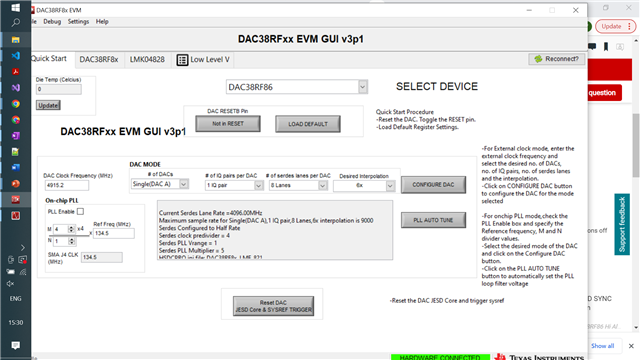

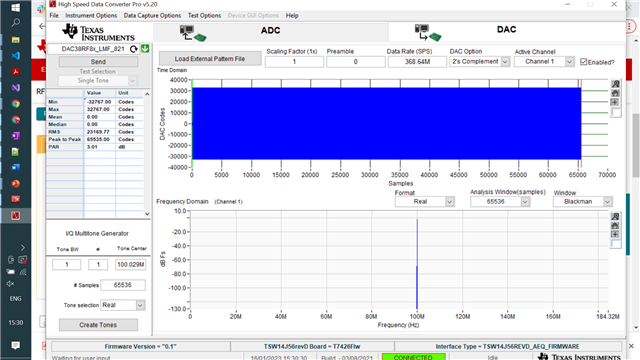

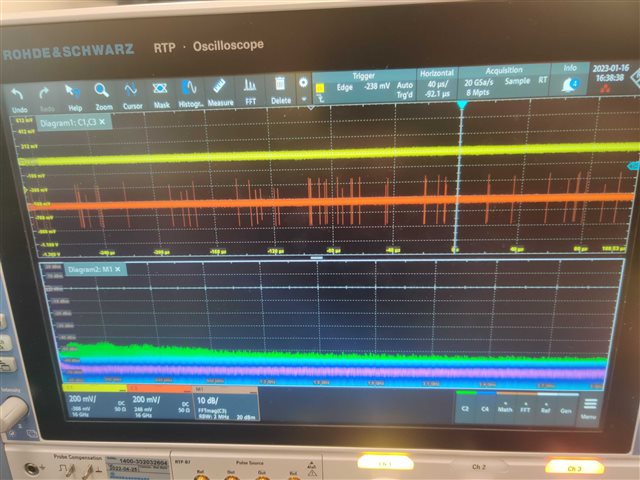

I am working with DAC38RF86EVM connected with TSW1456 Rev E where DAC is being used for waveform generation. I wanted to use DAC without supplying with an external clock to it, thus using the On-Board VCXO Clock Mode (CMODE4) as mentioned in the documentation. However, while reading through the document, the setup examples and steps shown are only shown for two modes : Direct External Clock Mode With High Amplitude Clock (CMODE1) and On-Chip PLL Clock Mode (CMODE3). I was trying to run the setup based on the instructions of CMODE3 and changing the bits required for VCXO Clock mode, however I am still unable to generate pattern using DAC in the same mode. Is there any separate documentation available for the VCXO mode or the changes required for it both hardware/ software , or is it very close to the On Chip PLL Clock mode minus the external clock?

Thanks for your consideration and looking forward to your response.

Thanks and Regards,

Vaibhav Jain.