Good day to all!

We are trying to work with AFE7950EVM and Xilinx KCU105.

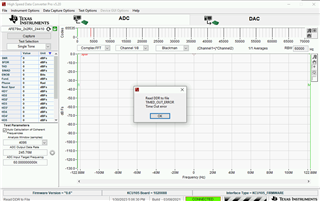

We follow the steps of "AFE79xx EVM Bring-up" video, but when we click on the "Capture" button in HSDC software we get an error: "Read DDR to file. TIMED_OUT_ERROR".

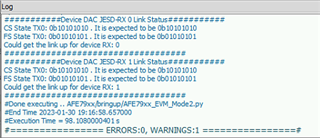

There are no errors in Latte log.

State of the LEDs on the KCU105 board:

0 - OFF (Rx SYNC)

1 - ON (Tx SYNC)

2 - ON (Rx Reset done)

3 - Flashing (DRP CLK)

4 - Flashing (DXI CLK)

5 - Flashing (TX/RX CORECLK)

6 - Flashing (GT REFCLK)

7 - OFF (TX EMPTY)

We tried to change number of samples (HSDC capture option), Invert Sync Polarity and Invert Serdes Data, but the error still remains.

GTXCLK on AFE7950EVM board is correct, CLK_LAO is the same, 245.76 MHz. FMC VADJ is always 1.8 V. Eye diagrams on all lines are good. AFE7950EVM board power supply is 5V and current limit is 5A.

We use Latte v5.6 and HSDC v5.20.

What could be the problem?

There may be an error in the AFE settings in the INI file?