Part Number: AFE7900EVM

Other Parts Discussed in Thread: AFE7900

Dear support,

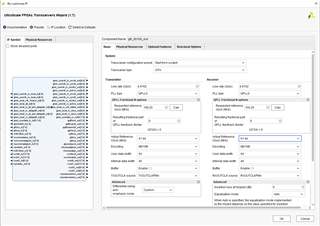

I have created this thread to aggregate my partial issues. I have an AFE7900EVM board with a ZCU102 board for parameter evaluation. I now need to operate the AD converter with all 4 ADC channels and decimation = 48. For the configuration of LMK and AFE7900, I use AFE79xx GUI (Latte) and for ZCU102 the provided reference design. The reference design (DDC = 4, Lanerate = 12 Gbps, 64/66 encoding, etc.) works well.

My question is: What needs to be modified - both on the JESD204 TI IP and GTH side, as well as in Python within AFE79xx? All my attempts have failed and the link has never been established.

E.g.:

1) Lanerate shoud be 4.9152 Gbps (is it correct?)

2) FPGA ref. clock shoud be 61.44 MHz (but I was not able to reach this value in Latte GUI - error message occured)

3) Lanes = 2

4) Encoding = 8B10B

5) And what about other parameters? (E, F, K, ...)?

Configuration script: TI_IP_5Gbps_DDC48.py

Thanks for your advice.