Other Parts Discussed in Thread: TSW14J58EVM, AFE8000

AFE80xxCatLibrary spi - USB Instrument created. resetDevice Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. Kintex RegProgrammer - USB Instrument created. FPGA reset - USB Instrument created. Power Card - USB Instrument created. Version : 0x104204b Connected to Capture Card Loaded Libraries Loaded Configuration: AFE8000_SampleConfig.xlsx Refreshed the GUI. #================ ERRORS:0, WARNINGS:0 ================# Programing FPGA .... Resetting FPGA Pin. Version : 0x101204c Connected to Capture Card FPGA Tx did not capture sysref FPGA Rx did not capture sysref Setting RBD to: 11 ###########Device DAC JESD-RX 0 Link Status########### Errors=0b11000000; Got errors: EoMB alignment error; EoEMB alignment error; Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b10101010 BUF State TX0: 0b00000000 . It is expected to be 0b11111111 Couldn't get the link up for device RX: 0 ################################### DAC Start FPGA Tx did not capture sysref FPGA Rx did not capture sysref Setting RBD to: 11 ###########Device DAC JESD-RX 0 Link Status########### Errors=0b11000000; Got errors: EoMB alignment error; EoEMB alignment error; Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good. Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good. CS State TX0: 0b00000000 . It is expected to be 0b10101010 BUF State TX0: 0b00000000 . It is expected to be 0b11111111 Couldn't get the link up for device RX: 0 ################################### DAC Start

Hello,

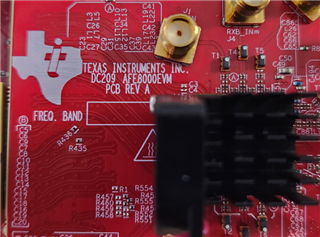

hardware: AFE8000EVM <--> DC182 TSW14J58

POWER:

AFE8000EVM 12DC (4A limited)

DC182 TSW14J58 5VDC(5A limited)

INPUT SIG:

10MHz 10dBm from sig gen to AFE8000EVM J18 LMK_CLKIN

OUTPUT SIG:

SMA connector to AFE8000EVM J13 TXA_OUT

CONTROL:

2x USB DC182 TSW14j58evm (1 is SS USB and is connected to an adequate SS Port on the computer)

1x USB AFE8000EVM

Please note that the DC182 TSW14j58EVM has had the firmware updated to the JESD204C version.

SOFTWARE:

AFE80xxCat.Exe

I am following the steps in the AFE8000EVM_Bringup_Guide power point and I am receiving errors at step 6, the errors are in the attached "eyeIssueLog.txt" file.

1) How do I check if the sysref is being captured on the Tx and Rx sides.

2) How do I check if the transmitter is sending data and the eye is good?

Thank you in advance.