Other Parts Discussed in Thread: LMK04828, AFE8000

I'm bring up the AFE8000EVM board, matched with the VPK120 board from Xilinx.

Synthesis of the FPGA using the reference design you provided seems to work.

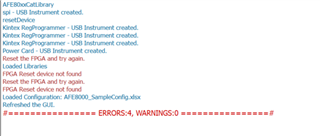

However when I download the image to the FPGA using vivado, I see the following messages:

I think the image is being loaded correctly - I've added some debug logic and that seems ok, but I don't know why I'm seeing these error messages.

Further debug suggests that the FPGA isn't receiving a clock from the AFE8000EVM, and it is being held in reset.

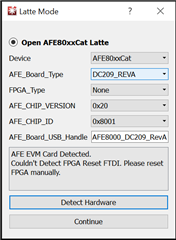

Looking at the AFE8000EVM board, when I try to connect to Latte I see the following at boot time:

The message suggests it can see the EVM card, but not the FPGA. I'm not sure if this is as a result of the configuration issues.

When I press "Continue" in Latte I see the following messages in the main GUI:

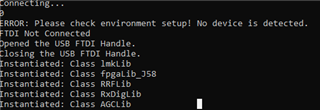

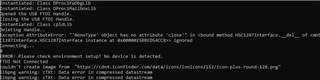

and these are the interesting parts of the console log:

Any assistance you can give here will be very helpful.

Other than that I have a couple of specific questions:

What is the required configuration order.

Do I need to have the FPGA programmed successfully before running Latte? If so, is the lack of a clock a problem?

Alternatively do I need to access Latte to allow it to program the LMK04828 before I configure the FPGA?

Can you confirm what clock frequency I need to supply to LMK_CLKIN? In the documentation supplied with the

release (RefDesign-Doc.pptx) there are references to 968MHz, but in the AFE8000EVMBringupGuide.pptx it suggests 10MHz.

We think the 10MHz is correct, but can you confirm?