Other Parts Discussed in Thread: AFE7444

Hi guys,

I am running AFE7444 EVM with Xilinx KCU105 .

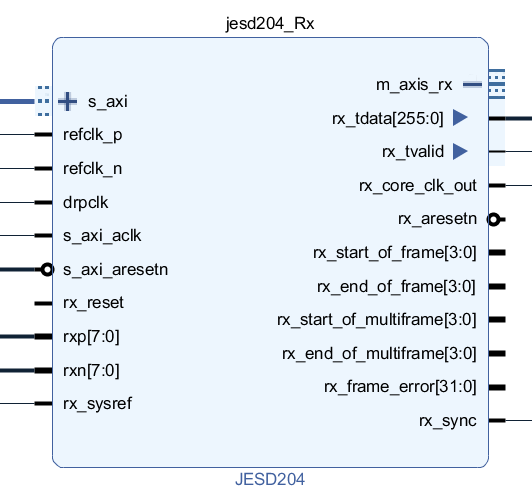

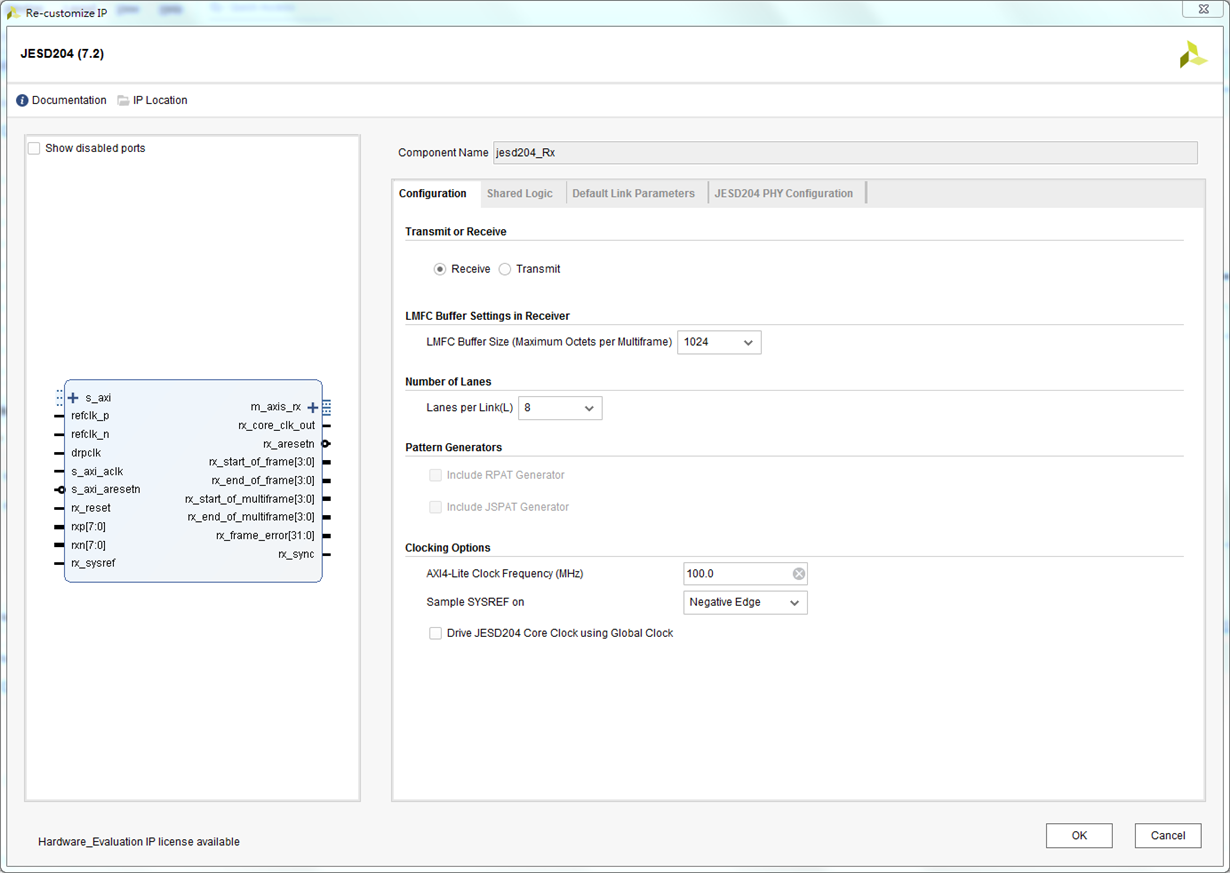

Xilinx JESD204 IP Parameter Setting:

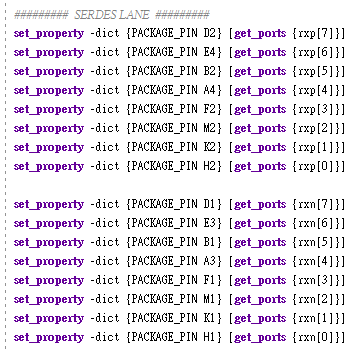

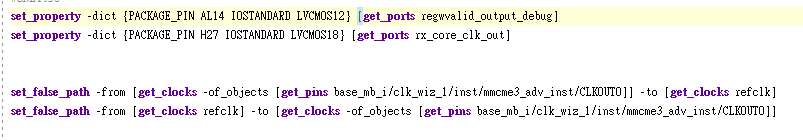

Constraints

Configuration Page.

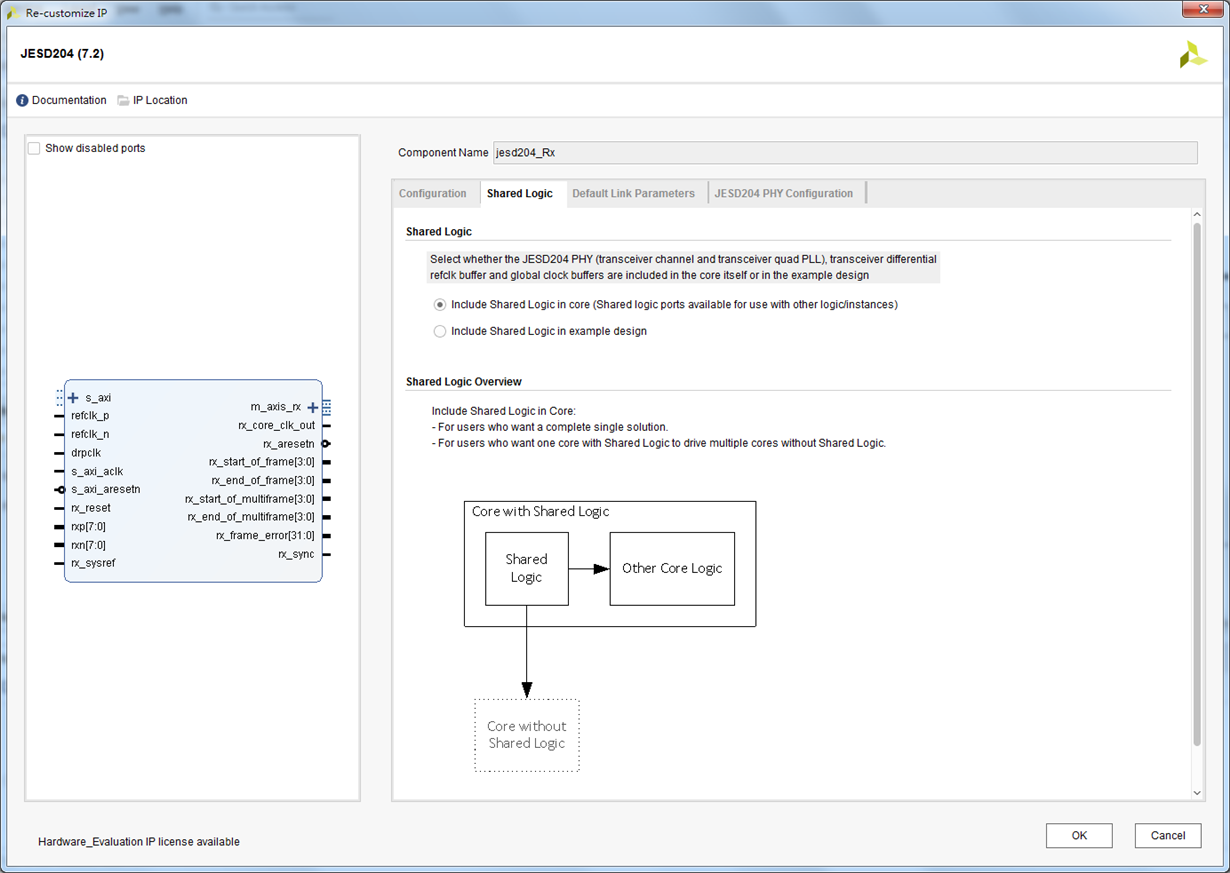

Share Logic Page.

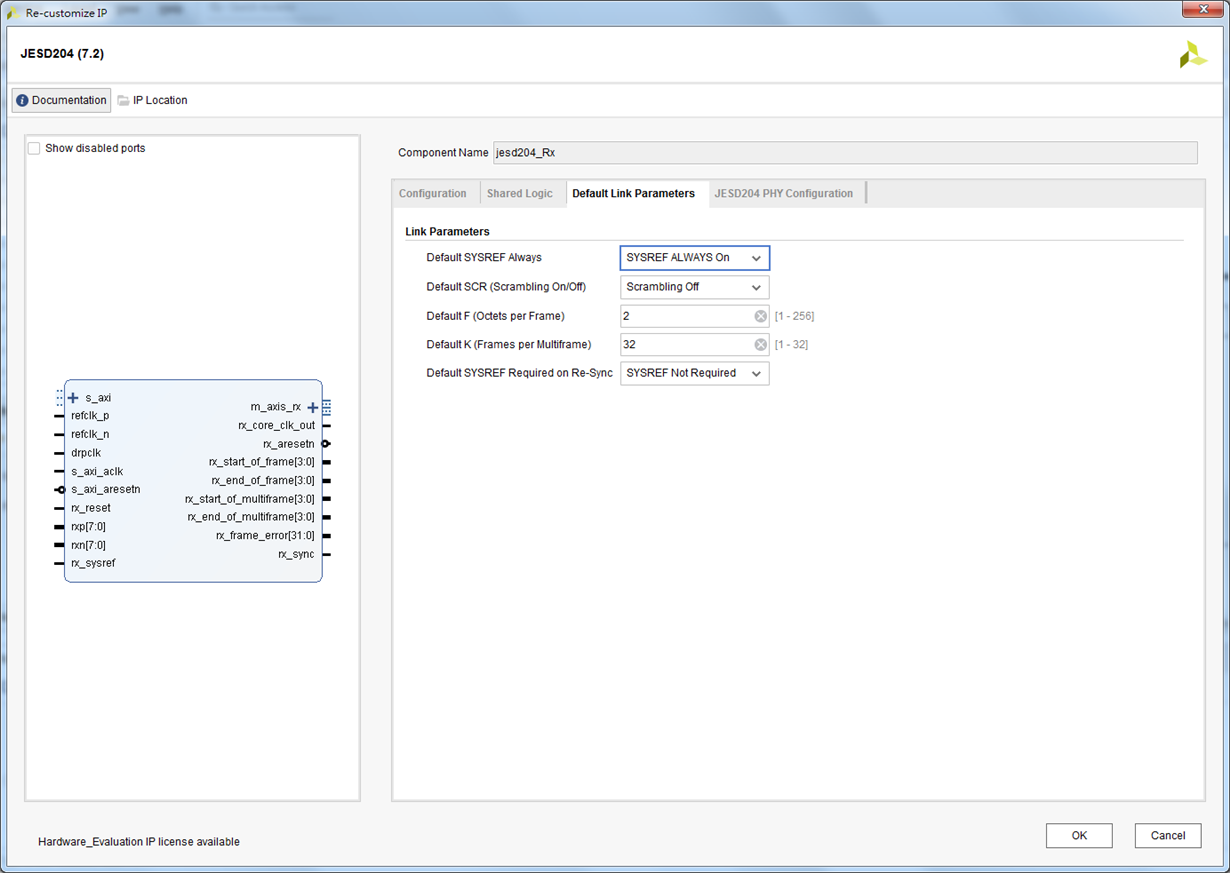

Default Link Parameters Page.

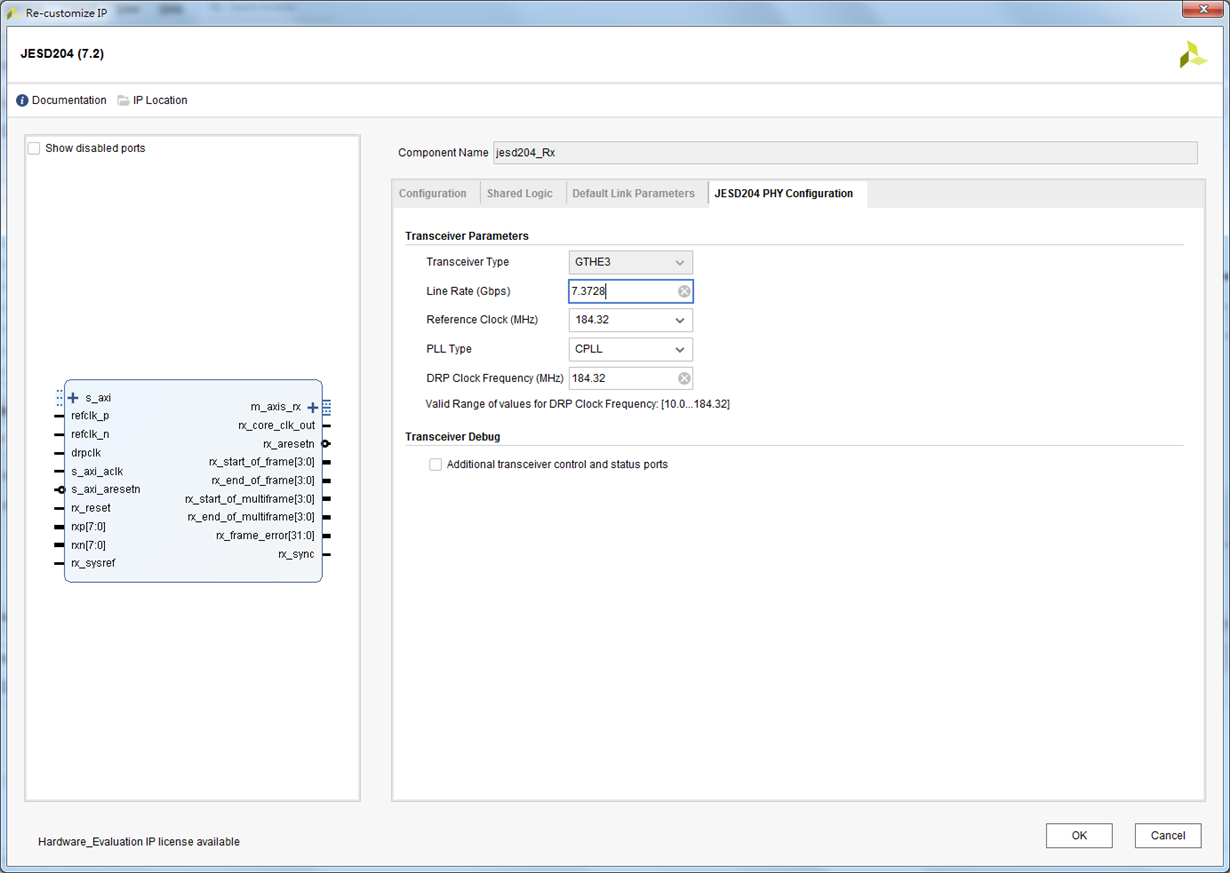

JESD204 PHY Configuration Page.

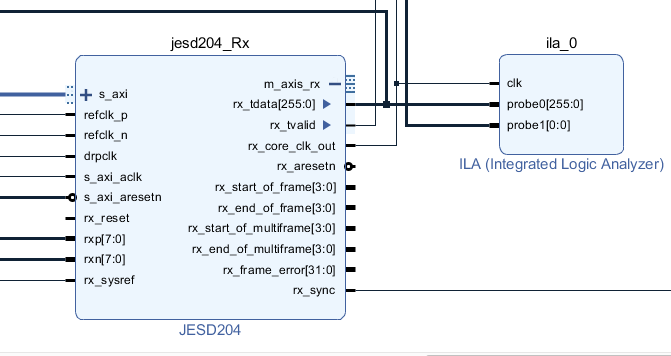

ILA Debug diagram

AFE7444EVM Parameter Setting:

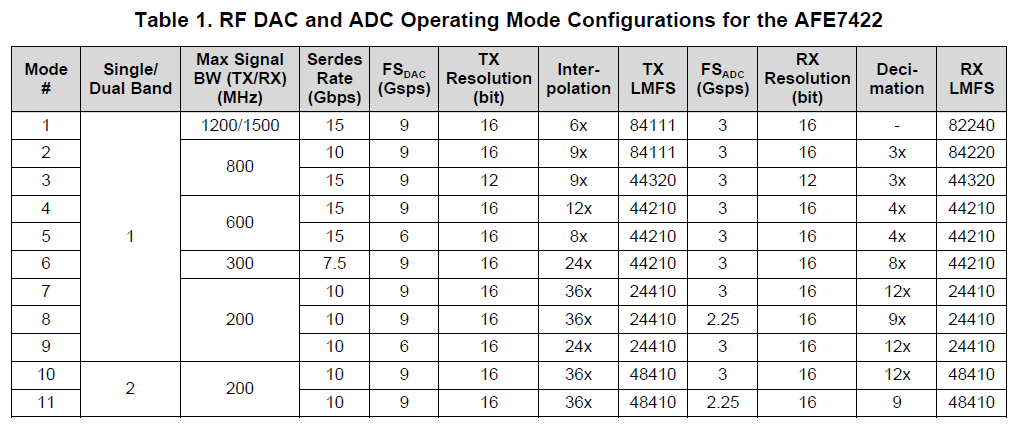

We’re using Mode#6, Rx LMFS at 44210.

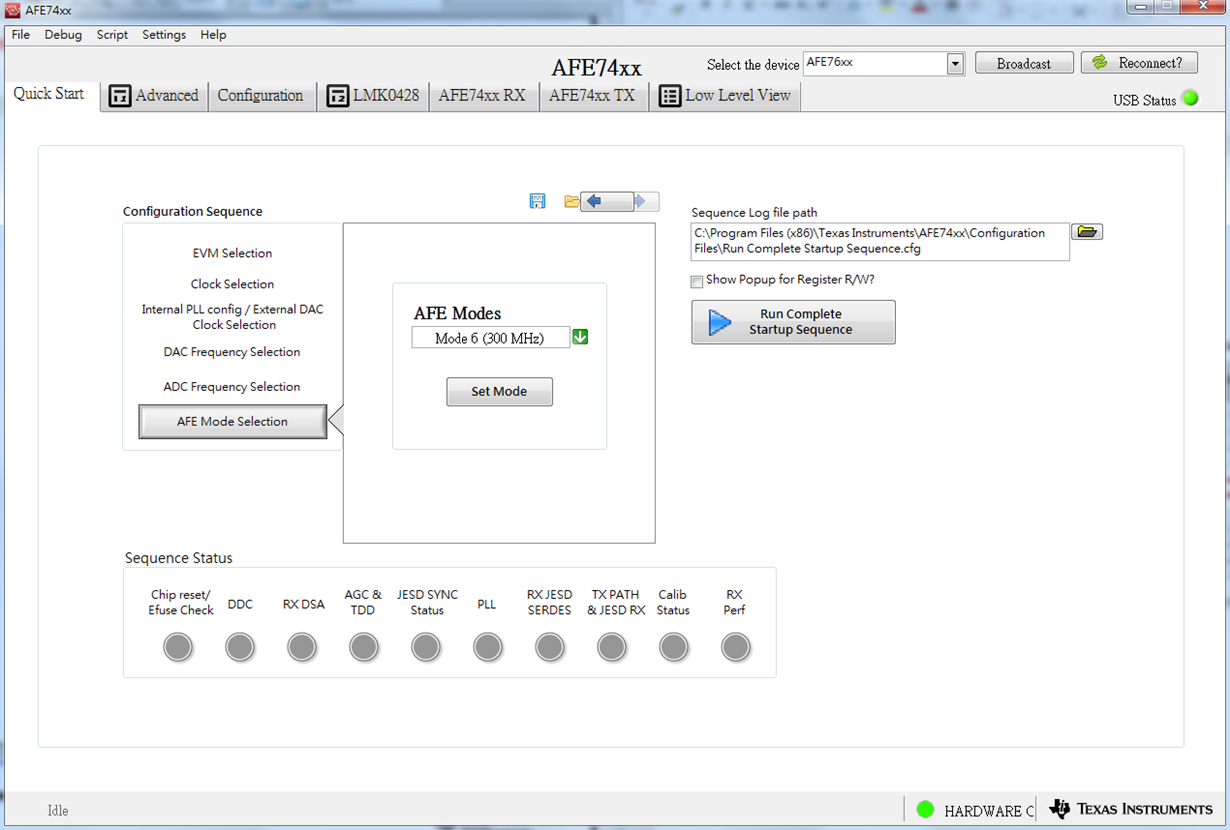

AFE74xx GUI Setting.

KCU105 detected refclk from AFE7444EVM is about 185MHz in selected Mode#6

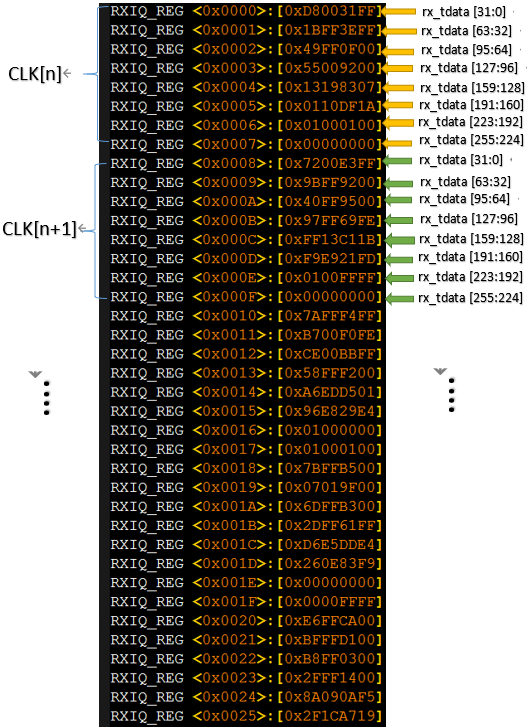

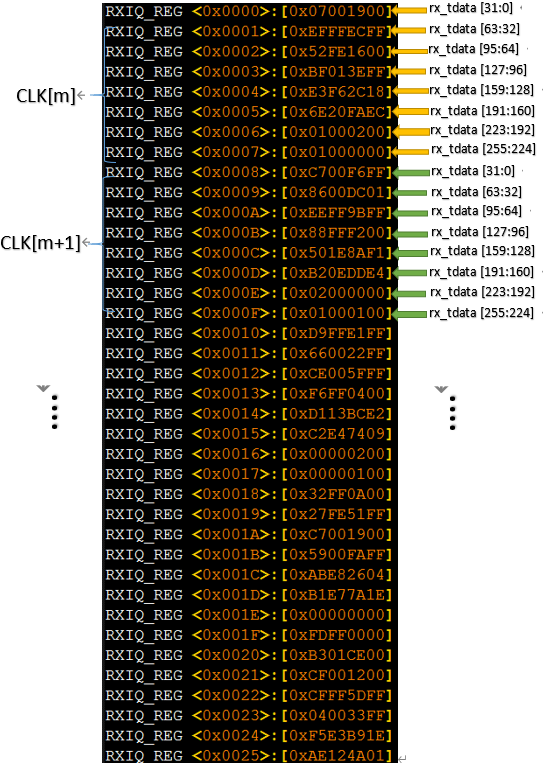

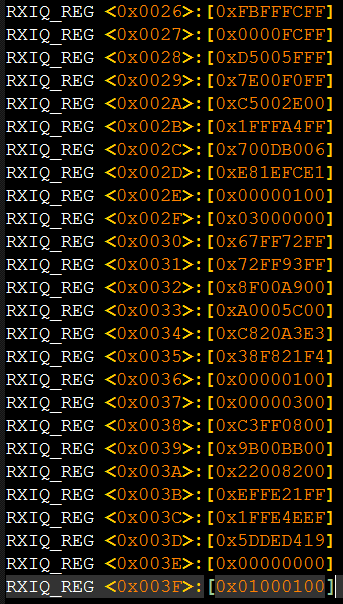

Rx_JESD Register Request (FPGA side)

JESD Reg addr < 0x38 > : JESD_Rx SYNC status

JESD Reg addr < 0x3C > : JESD_Rx Debug Status

Recive Serdes Lane data:

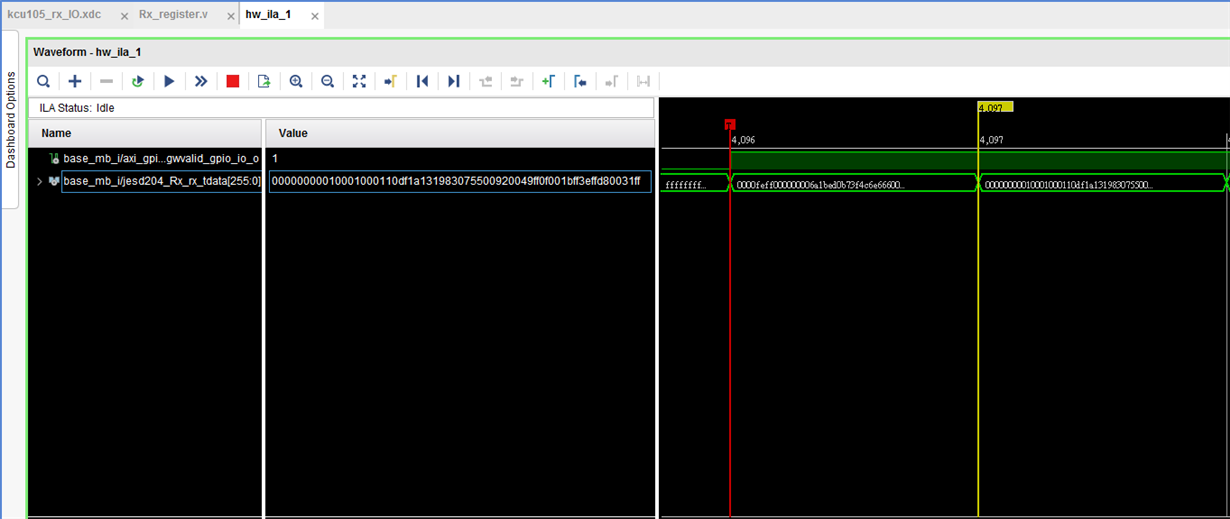

JESD rx_tdata[255:0]

AFE7444 A_IN1 ( J14 ) without RF in

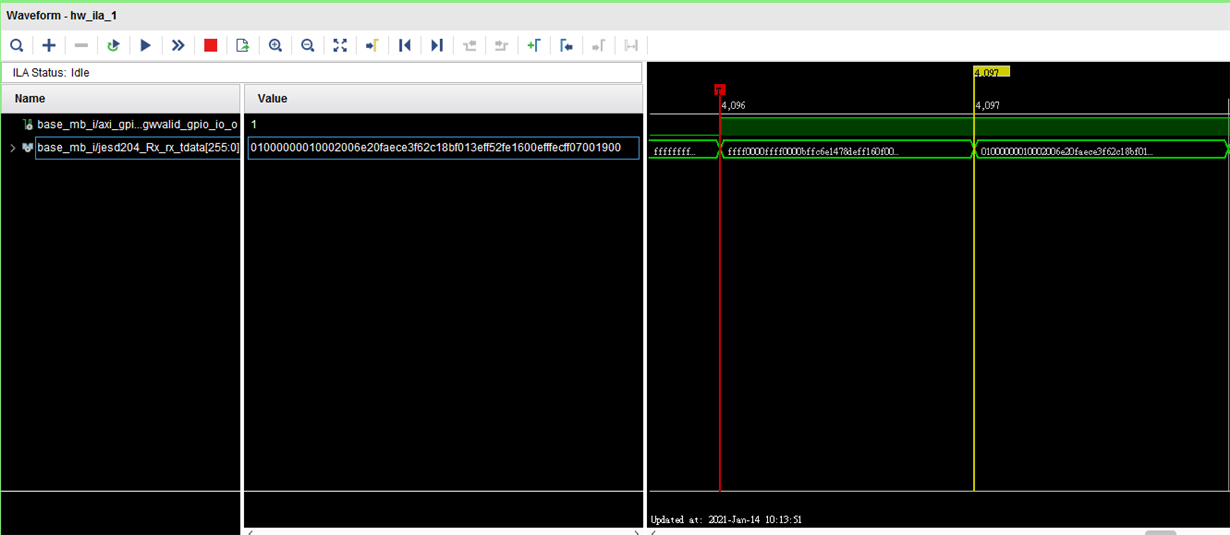

Vivado ILA

AFE7444 A_IN1 ( J14 ) with 3GHz RF single tone signal input.And Set AFE7444 Rx NCO 2990.

Xilinx ILA

Here are the 2 questions I've got as below:

- Rx sample rate is 3GHz, TI Mode#6 decimation is x8, so the data bandwidth is 3000/8 = 375MHz, and using *.cfg file which is TI provided. And read the register from AFE7444, is the refclk = 185 MHz right?

- How to separate the resolution of 256-bits rx_data to 4 channel (A, B, C, D) IQ data? (Both the scrambler of AFE7444 and KCU105 are confirmed to be closed)