Part Number: TRF372017

Hi Team,

My customer is evaluating TRF370217 EVM and has some issues that described as following. Please give us some advices.

We're currently testing the TRF372017 evaluation module.

EVM abnormal phenomenon need to be resolved.

Here were our testing environment:

Signal generator : Keysight VXG M9384B

Signal Analyzer : Keysight UXA N9040B

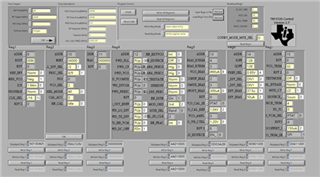

GUI setting(default):

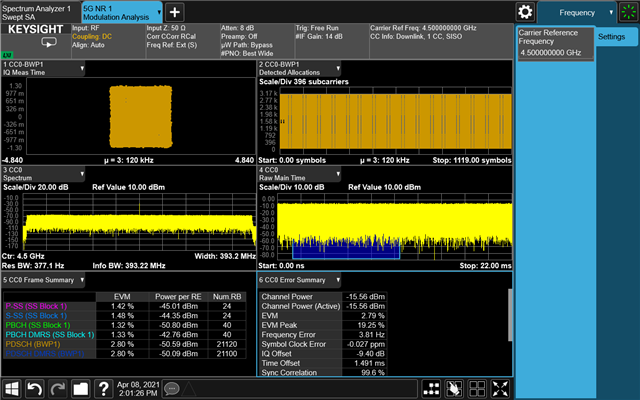

We measured EVM on TRF372017 evaluation board at 4.5GHz LO with a 100MHz wide 64QAM 5GNR baseband signal coming from signal generator.

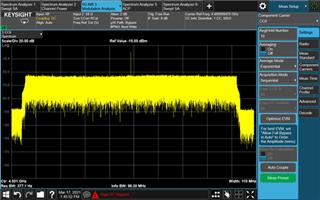

There was a high peak in the middle, and we couldn’t get the EVM(shown below).

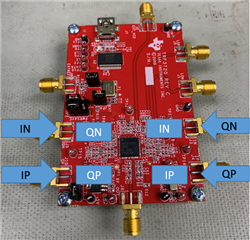

But once we switched the I/Q baseband input(IN←→QN,IP←→QP), the connection picture is as below.

we can get the poor EVM while still existing a DC offset. (shown below)

From the above situation ,

How can we eliminate the DC offset and get excellent EVM?

Also, we want to know the reason why we have to switch the I/Q baseband signal to get the EVM result.

Thanks a lot.

Vincent Chen